Yesterday I met with Michael Buehler-Garcia, Director of Marketing at Mentor Graphics for Calibre in Wilsonville, Oregon to get an update on what’s coming up at DAC, the premier conference and trade show for our industry.

IC Reliability and Prevention During Design with EDA Tools

IC device physics uncovers limits to reliable operation, so IC designers are learning to first identify and then fix reliability issues prior to tape-out. Here’ s a list of reliability issues to keep you awake at night:… Read More

Mentor’s New Emulator

Mentor announced the latest version of their Veloce emulator at the Globalpress briefing in Santa Cruz. The announcement is in two parts. The first is that they have designed a new custom chip with twice the performance and twice the capacity. It supports up to two billion gate designs and many software engineers. Surprisingly … Read More

Changing your IC Layout Methodology to Manage Layout Dependent Effects (LDE)

Smaller IC nodes bring new challenges to the art of IC layout for AMS designs, like Layout Dependent Effects (LDE). If your custom IC design flow looks like the diagram below then you’re in for many time-consuming iterations because where you place each transistor will impact the actual Vt and Idsat values, which are now a … Read More

Doing what others don’t do

Wally Rhines’ keynote at U2U, the Mentor users’ group meeting, was about Mentor’s strategy of focusing on what other people don’t do. This is partially a defensive approach, since Mentor has never had the financial firepower to have the luxury of focusing all their development on sustaining their products and then make … Read More

U2U Mentor Users’ Group

Mentor’s U2U user group meeting in Santa Clara is next week on April 12th at the Santa Clara Marriott. For those of you on the east coast the Waltham U2U is on May 16th, and for Europeans the Munich U2U will be on October 25th. Registration is open for both Santa Clara and Waltham, and there is a call for papers for Munich.

The day … Read More

Conquering the Big Data Challenges

Extrapolating the trends from last 20 years to the next ten suggests that we will be implementing a trillion transistors or more by 2020. At 20nm, with the chip sizes touching billions of transistors, the age old problem of how to implement a design in the most efficient manner remains unanswered. … Read More

3D-IC Testing – A 3D perspective to SoC

In my last article I talked about the physical design aspect of 3D-IC. Now looking at its verification aspect, it spans through a wide spectrum of test at hardware as well as software level. The verification challenge goes much beyond that of a SoC which is at a single plane. Even a typical SoC that comprises of a processor core, memory… Read More

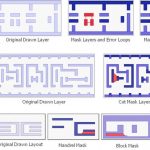

Double Patterning and Then The End of Lithography

I went to a couple more sessions at the Common Platform Technology Forum today, on 20nm double patterning and whatever will we do at 14nm. Basically, this is the end of planar transistors and the end of optical lithography. One session was by IBM scientists about process and one by Michael White of Mentor about double patterning. … Read More

Common Platform Technology Forum: Peering into the Future

Next Wednesday is the Common Platform Technology Forum. “Common Platform” is a name that only a committee could have come up with, giving no clue as to what it actually is. As you probably know, there are various process clubs sharing the costs of technology development (TD) and one of them consists of IBM, Samsung and… Read More