Dan is joined by sureCore CEO Paul Wells. Paul has worked in the semiconductor industry for over 25 years including two years as director of engineering for Pace Networks, where he led a multidisciplinary, 70 strong product development team creating a broadcast quality video & data mini-headend. Before that, he worked for… Read More

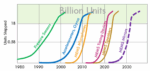

AI explosion is clearly driving semi-industry since 2020. AI processing, based on GPU, need to be as powerful as possible, but a system will reach optimum only if it can rely on top interconnects. The various sub-system need to be interconnected with ever more bandwidth and lower latency, creating the need for ever advanced protocol… Read More

Many know Arteris as the “network-on-chip”, or NoC, company. Through acquisitions and forward-looking development, the footprint for Arteris has grown beyond smart interconnect IP. At DAC this year, Arteris highlighted its latest expansion with a new SoC integration automation product called Magillem Packaging. The announcement… Read More

Last month, Lj Ristic delivered an invited talk on MEMS technology as a driving force at the Laser Display and Lighting Conference 2025, held at Trinity College Dublin. His talk included a review of some major successes of MEMS industry. We used that occasion to talk to him and discuss some major achievements and the status of MEMS… Read More

Edge AI is rapidly transforming how intelligent solutions are designed, from smart home devices to autonomous vehicles, healthcare gadgets, and industrial IoT. Yet, architects, chip designers, and product managers frequently grapple with a common and daunting challenge: creating efficient, high-performance AI solutions… Read More

In today’s data-driven systems—from cloud storage and AI accelerators to automotive logging and edge computing—every byte counts. The exponential growth in data volumes, real-time processing demands, and constrained bandwidth has made efficient, lossless data compression a mission-critical requirement. Software-based… Read More

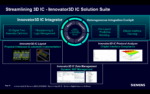

In a major announcement at the 2025 Design Automation Conference (DAC), Siemens EDA introduced a significant expansion to its electronic design automation (EDA) portfolio, aimed at transforming how engineers design, validate, and manage the complexity of next-generation three-dimensional integrated circuits (3D ICs).… Read More

Dan is joined by Andrea Gallo, CEO of RISC-V International, the non-profit home of the RISC-V instruction set architecture standard, related specifications, and stakeholder community. Prior to joining RISC-V International, Gallo worked in leadership roles at Linaro for over a decade. He built Linaro’s server engineering… Read More

In 2003, legendary computer architect Michael J. Flynn issued a warning that most of the industry wasn’t ready to hear. The relentless march toward more complex CPUs—with speculative execution, deep pipelines, and bloated instruction handling—was becoming unsustainable. In a paper titled “Computer Architecture … Read More

Qualifying an AI-class RISC-V SoC demands proving that wide vectors, deep caches, and high-speed I/O operate flawlessly long before tape-out. At the recent Andes RISC-V Conference, Andes Technology and S2C showcased this by successfully booting a lightweight large language model (LLM) inference on a single S2C Prodigy™ S8-100… Read More

Facing the Quantum Nature of EUV Lithography