Accurate, complete, and consistent technical documentation is a critical element of success for any embedded system design project. This includes IP, SoCs, and the associated hardware and software infrastructure. When documentation contains errors, the consequences go beyond engineering inefficiency. Errors that drive… Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

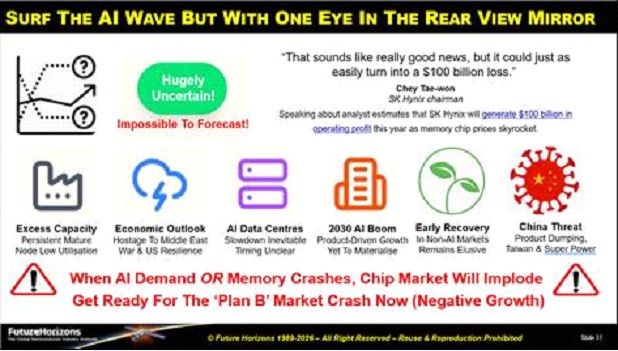

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read MoreBronco AI Webinar: Full-Chip SoC Debug in 15 Minutes

A single bug on a full-chip SoC can pull engineers off roadmap work for days or even weeks. It involves massive waveforms, thousands of files of RTL and UVM, and dense specs that aren’t always perfect. Finding these bugs have always been a matter of engineer-hours and how well knowledge diffuses through the organization.

Bronco … Read More

Europe is Getting Serious About ASIC Innovation

I was born in the UK (then still a part of Europe), so always eager to see them succeed. But I must admit that past behavior has reinforced the view that the EU’s only active “contribution” to progress is regulation. However this seems to be changing in multiple interesting ways. On a grand scale, the Nordic economic model is taking … Read More

Siemens EDA Expands AI and Advanced Packaging Collaboration with TSMC

At the recent TSMC Technology Symposium 2026, Siemens EDA reinforced its position as one of the key ecosystem partners supporting TSMC in the race toward AI-driven semiconductor design, advanced packaging, and next-generation process technologies. The annual forum has become one of the semiconductor industry’s most important… Read More

Semidynamics Secures a Strategic Investment to Advance Memory-Centric AI Inference Chips

In the rapidly evolving world of artificial intelligence hardware, memory bandwidth and data movement have become just as important as raw compute power. Addressing this challenge head-on, Semidynamics has announced a strategic investment aimed at accelerating the development of its next-generation memory-centric AI … Read More

Quantum Gathering Momentum Amid Concerns for the Grid

I posted recently on an eye-catching advance in quantum computing, around neutral atom systems which might accelerate the transition to production-grade fault-tolerant quantum computing (QC). There are some further updates on this front, also I listened in on a panel considering quantum-based hacking vulnerability in the… Read More

PQShield unveils ultra-small PQC embedded security breakthroughs at Embedded World 2026

As the threat of quantum computing to modern cybersecurity becomes increasingly real, the technology industry is accelerating efforts to develop cryptographic systems capable of resisting quantum attacks. One of the most significant developments in this field was presented at Embedded World 2026 in Nuremberg, Germany, … Read More

Closing the Silicon Realization Gap: From Static DFM to Governance for Lifecycle (GFL)

The semiconductor industry has achieved extraordinary mastery in silicon signoff. Modern EDA environments can now optimize timing closure, physical verification, IR/EM behavior, routing density, thermal interaction, and increasingly even design-space exploration through AI-assisted implementation flows. Crossing… Read More

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scaling

imec announced that IC-Link by imec has joined the TSMC 3DFabric Alliance, a strategically important move that reflects the semiconductor industry’s transition from traditional monolithic scaling toward heterogeneous integration, chiplet architectures, and advanced packaging-driven system optimization. The partnership… Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting

The paper, Industrial Defectivity Prediction (IDP) V6: A Two-Layer Yield Cliff Framework for Cross-Industry Mass-Production Forecasting, presents a generalized industrial yield-modeling architecture that extends the classical Negative Binomial framework through a two-layer phenomenological structure designed … Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior