Naveen Verma, Ph.D., is the CEO and Co-founder of EnCharge AI, the only company to have developed robust and scalable analog in-memory computing technology essential for advanced AI deployments, from edge to cloud. Dr. Verma co-founded EnCharge AI in 2022, building on six years of research and five generations of prototypes … Read More

Artificial Intelligence

ChipAgents Tackles Debug. This is Important

Innovation is never ending in verification, for performance, coverage, connection to verification plans and other aspects of DV. But debug, accounting for 40% of the verification cycle, has remained stubbornly resistant to significant automation. Debug IDEs help to visualize but don’t address the core problem: given a failure,… Read More

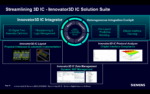

Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and Analysis

In a major announcement at the 2025 Design Automation Conference (DAC), Siemens EDA introduced a significant expansion to its electronic design automation (EDA) portfolio, aimed at transforming how engineers design, validate, and manage the complexity of next-generation three-dimensional integrated circuits (3D ICs).… Read More

CEO Interview with Faraj Aalaei of Cognichip

Faraj Aalaei is a successful visionary entrepreneur with over 40 years of distinguished experience in communications and networking technologies. As a leading entrepreneur in Silicon Valley, Faraj was responsible for building and leading two semiconductor companies through IPOs as a founder and CEO.

Post acquisition of … Read More

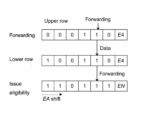

Rethink Scoreboards to Supercharge AI-Era CPUs

By Dr. Thang Minh Tran, CEO/CTO Simplex Micro

Today’s AI accelerators—whether built for massive data centers or low-power edge devices—face a common set of challenges: deep pipelines, complex data dependencies, and the high cost of speculative execution. These same concerns have long been familiar in high-frequency microprocessor… Read More

Reachability in Analog and AMS. Innovation in Verification

Can a combination of learning-based surrogate models plus reachability analysis provide first pass insight into extrema in circuit behavior more quickly than would be practical through Monte-Carlo analysis? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot

In 2003, legendary computer architect Michael J. Flynn issued a warning that most of the industry wasn’t ready to hear. The relentless march toward more complex CPUs—with speculative execution, deep pipelines, and bloated instruction handling—was becoming unsustainable. In a paper titled “Computer Architecture … Read More

DAC News – A New Era of Electronic Design Begins with Siemens EDA AI

AI is the centerpiece of DAC this year. How to design chips to bring AI algorithms to life, how to prevent AI from hacking those chips, and of course how to use AI to design AI chips. In this latter category, there were many presentations, product announcements and demonstrations. I was impressed by many of them. But an important observation… Read More

Arteris Expands Their Multi-Die Support

I am tracking the shift to multi-die design, so it’s good to see Arteris extend their NoC expertise, connecting chiplets across an interposer. After all, network connectivity needs don’t stop at the boundaries of chiplets. A multi-die package is at a logical level just a scaled-up SoC for which you still need traffic routing and… Read More

Caspia Technologies at the 2025 Design Automation Conference #62DAC

Security will be an important topic at DAC this year. The hardware root of trust is the foundation of all security for complex systems implementing AI workloads. Thanks to new and sophisticated techniques the hardware root of trust is now vulnerable and must be protected. But adding deep security verification to existing design… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot