Alchip Technologies has recently reported significant progress in the development of advanced 2nm ASICs, positioning itself as a leader in next-generation semiconductor design for AI and HPC. The announcement highlights Alchip’s efforts to commercialize cutting-edge chip technologies and deliver highly customized … Read More

Synopsys Advances Hardware Assisted Verification for the AI Era

At the 2026 Synopsys Converge Event, Synopsys announced a broad set of new products and platform upgrades, with its hardware-assisted verification (HAV) announcement emerging as a key highlight within that lineup. A key aspect of this announcement was moving beyond a hardware centric model to a more scalable, programmable … Read More

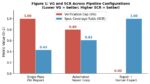

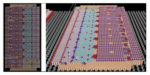

Scaling Multi-Die Connectivity: Automated Routing for High-Speed Interfaces

This article concludes the three-part series examining key methodologies required for successful multi-die design. The first article Reducing Risk Early: Multi-Die Design Feasibility Exploration focused on feasibility exploration and early architectural validation, while the second article Building the Interconnect… Read More

Podcast EP335: The Far Reaching Impact of UCIe with Dr. Debendra Das Sharma

Daniel is joined by Dr. Debendra Das Sharma, a Senior Fellow and Chief I/O architect in the Data Platforms and Artificial Intelligence Group at Intel. He is a member of the National Academy of Engineering (NAE), Fellow of IEEE, and Fellow of International Academy of AI Sciences. He is a leading expert on I/O subsystem and interface… Read More

Qnity and Silicon Catalyst Light a Path to Success at the Chiplet Summit

The Chiplet Summit recently concluded. Multi-die heterogeneous design is a hot topic these days and chiplets are a key enabler for this trend. The conference was noticeably larger this year. There were many presentations and exhibits that focused on areas such as how to design chiplets, what standards are important, how to integrate… Read More

Why Your LLM-Generated Testbench Compiles But Doesn’t Verify: The Verification Gap Problem

By Vikash Kumar, Senior Verification Architect | Arm | IEEE Senior Member.

The Problem Every Verification Engineer Recognizes

You ask an LLM to generate a UVM testbench. It produces 25 files. Everything compiles. You run the simulation — and nothing happens. The scoreboard reports zero checks. The slave driver stops after 10… Read More

Keynote: On-Package Chiplet Innovations with UCIe

In the rapidly evolving landscape of semiconductor technology, the Universal Chiplet Interconnect Express (UCIe) emerges as a groundbreaking open standard designed to revolutionize on-package chiplet integrations. Presented by Dr. Debendra Das Sharma, Chair of the UCIe Consortium and Intel Senior Fellow, at the Chiplet… Read More

Reducing Risk Early: Multi-Die Design Feasibility Exploration

The semiconductor industry is entering a new era in system design. As traditional monolithic scaling approaches its economic and physical limits, multi-die architectures are emerging as a primary pathway for delivering continued improvements in performance, power efficiency, and integration density. By distributing … Read More

Building the Interconnect Foundation: Bump and TSV Planning for Multi-Die Systems

The first article in this series examined how feasibility exploration enables architects to evaluate multi-die system configurations while minimizing early design risk. Once architectural decisions are validated, designers must translate conceptual connectivity requirements into physical interconnect infrastructure.… Read More

Designing the Future: AI-Driven Multi-Die Innovation in the Era of Agentic Engineering

At the 2026 Chiplet Summit, Synopsys presented a bold vision for the future of semiconductor innovation: AI-driven multi-die design powered by agentic intelligence. As the semiconductor industry shifts rapidly toward chiplet-based architectures and 3D stacking, the complexity of design, verification, and system integration… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea