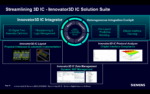

The semiconductor industry is rapidly moving beyond traditional 2D packaging, embracing technologies such as 3D integrated circuits (3D ICs) and 2.5D advanced packaging. These approaches combine heterogeneous chiplets, silicon interposers, and complex multi-layer routing to achieve higher performance and integration.… Read More

Electronic Design Automation

Building Trust in Generative AI

AI technology was prevalent at DAC 2025, but can we really trust what Generative AI (GenAI) is producing? Vishal Moondhra, VP of Solutions Engineering from Perforce talked about this topic in the Exhibitor Forum on Monday, so I got a front row seat to learn more.

Vishal started out by introducing the four challenges and risks of using… Read More

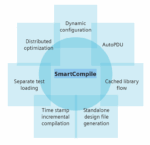

Revolutionizing Simulation Turnaround: How Siemens’ SmartCompile Transforms SoC Verification

In the race to deliver ever-larger SoCs under shrinking schedules, simulation is becoming a bottleneck. With debug cycles constrained by long iteration times—even for minor code changes—teams are finding traditional flows too rigid and slow. The problem is further magnified in continuous integration and continuous deployment… Read More

ChipAgents Tackles Debug. This is Important

Innovation is never ending in verification, for performance, coverage, connection to verification plans and other aspects of DV. But debug, accounting for 40% of the verification cycle, has remained stubbornly resistant to significant automation. Debug IDEs help to visualize but don’t address the core problem: given a failure,… Read More

Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and Analysis

In a major announcement at the 2025 Design Automation Conference (DAC), Siemens EDA introduced a significant expansion to its electronic design automation (EDA) portfolio, aimed at transforming how engineers design, validate, and manage the complexity of next-generation three-dimensional integrated circuits (3D ICs).… Read More

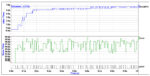

Jitter: The Overlooked PDN Quality Metric

Bruce Caryl is a Product Specialist with Siemens EDA

The most common way to evaluate a power distribution network is to look at its impedance over the effective frequency range. A lower impedance will produce less noise when transient current is demanded by the IC output buffers. However, this transient current needs to be provided… Read More

Reachability in Analog and AMS. Innovation in Verification

Can a combination of learning-based surrogate models plus reachability analysis provide first pass insight into extrema in circuit behavior more quickly than would be practical through Monte-Carlo analysis? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys… Read More

Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping System

Qualifying an AI-class RISC-V SoC demands proving that wide vectors, deep caches, and high-speed I/O operate flawlessly long before tape-out. At the recent Andes RISC-V Conference, Andes Technology and S2C showcased this by successfully booting a lightweight large language model (LLM) inference on a single S2C Prodigy™ S8-100… Read More

DAC News – A New Era of Electronic Design Begins with Siemens EDA AI

AI is the centerpiece of DAC this year. How to design chips to bring AI algorithms to life, how to prevent AI from hacking those chips, and of course how to use AI to design AI chips. In this latter category, there were many presentations, product announcements and demonstrations. I was impressed by many of them. But an important observation… Read More

Podcast EP293: 3DIC Progress and What’s Coming at DAC with Dr. John Ferguson and Kevin Rinebold of Siemens EDA

Dan is joined by Dr. John Ferguson, Director of Product Management for the Calibre nmDRC and 3DIC related products for Siemens EDA. John has worked extensively in the area of physical design verification. Holding several patents, he is also a frequent author in the physical design and verification domain. Current activities … Read More

Facing the Quantum Nature of EUV Lithography