You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 386

[name] => Semiconductor Services

[slug] => semiconductor-services

[term_group] => 0

[term_taxonomy_id] => 386

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 1128

[filter] => raw

[cat_ID] => 386

[category_count] => 1128

[category_description] =>

[cat_name] => Semiconductor Services

[category_nicename] => semiconductor-services

[category_parent] => 0

[is_post] =>

)

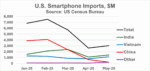

Our Semiconductor Intelligence June Newsletter showed how U.S. imports of smartphones have been on a downward trend since January 2025, led by China. Other key electronic products have also experienced sharp drops in U.S. imports from China.F

U.S. smartphone imports in May 2025 were $3.03 billion, up slightly from April but … Read More

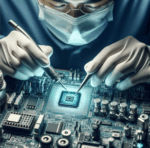

AI explosion is clearly driving semi-industry since 2020. AI processing, based on GPU, need to be as powerful as possible, but a system will reach optimum only if it can rely on top interconnects. The various sub-system need to be interconnected with ever more bandwidth and lower latency, creating the need for ever advanced protocol… Read More

In AI it is easy to be distracted by hype and miss the real advances in technology and adoption that are making a difference today. Accellera hosted a panel at DAC on just this topic, moderated by Dan Nenni (Mr. SemiWiki). Panelists were: Chuck Alpert, Cadence’s AI Fellow driving cross-functional Agentic AI solutions throughout… Read More

It was my pleasure to meet with Vamshi Kothur and the Tuple team at #62DAC for a briefing on their Tropos platform and Omni, a new multi-cloud optimizer. The conferences this year have been AI infused with exciting new technologies but one of the lingering questions is: How will the existing semiconductor design IT infrastructure… Read More

If you’ve spent a lot of time in the chip or EDA business, “design” typically means chip design. These days it means heterogeneous multi-chip design. If you’ve spent time developing end products, “design” has a much broader meaning. Chips, subsystems, chassis and product packaging are in focus. This is just a short list if you consider… Read More

It’s now difficult to remember when we didn’t reuse our own IP and didn’t have access to extensive catalogs of commercial IP. But reuse comes with a downside – without modification we can’t finetune IP specs to exactly what we want in a current design. We’re contractually limited in how we can adapt commercial IP, however vendors … Read More

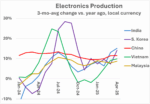

Electronics production in key Asian countries has been steady to increasing in the last several months. In April 2025, China electronics production three-month-average change versus a year ago (3/12) was 11.5%, up from 9.5% in January but below the average 3/12 of 12% in 2024. India showed the strongest growth, with 3/12 of 15%… Read More

Ollie is a commercially astute senior leader with over 20 years of experience in strategy, business development and sales across the technology and engineering sectors, with a strong track record in scaling businesses and driving growth. He has held commercial leadership roles in FTSE 100, private equity-backed, and startup… Read More

Tuple Technologies delivers Tropos, a platform automating IT infrastructure across Cloud, Hybrid or On-prem and DevSecOps for semiconductor IC, FPGA, and system design, optimizing costs and cybersecurity.

Attendees who step into the Tuple Technologies booth during DAC (Booth #1237) will see demonstrations of its Tropos … Read More

WSTS reported 1st quarter 2025 semiconductor market revenues of $167.7 billion, up 18.8% from a year earlier and down 2.8% from the prior quarter. The first quarter of 2025 was weak for most major semiconductor companies. Ten of the sixteen companies in the table below had declines in revenue versus 4Q 2024, ranging from -0.1% from… Read More

TSMC N3 Process Technology Wiki