Digital design and verification is well understood by EDA vendors and IC designers, however mixed-signal design and verification is more challenging, because the continuous nature of analog signals requires more compute resources and specialized design skills. Siemens EDA has a unique offering in what they call Symphony, as it connects the most popular commercial digital simulators to their Analog Fast SPICE (AFS) circuit simulator to enable mixed-signal simulation quickly and accurately. I attended a webinar on Symphony last month and describe my findings in this blog. If you missed it, you can now view the webinar on-demand: Symphony for Mixed-Signal Verification.

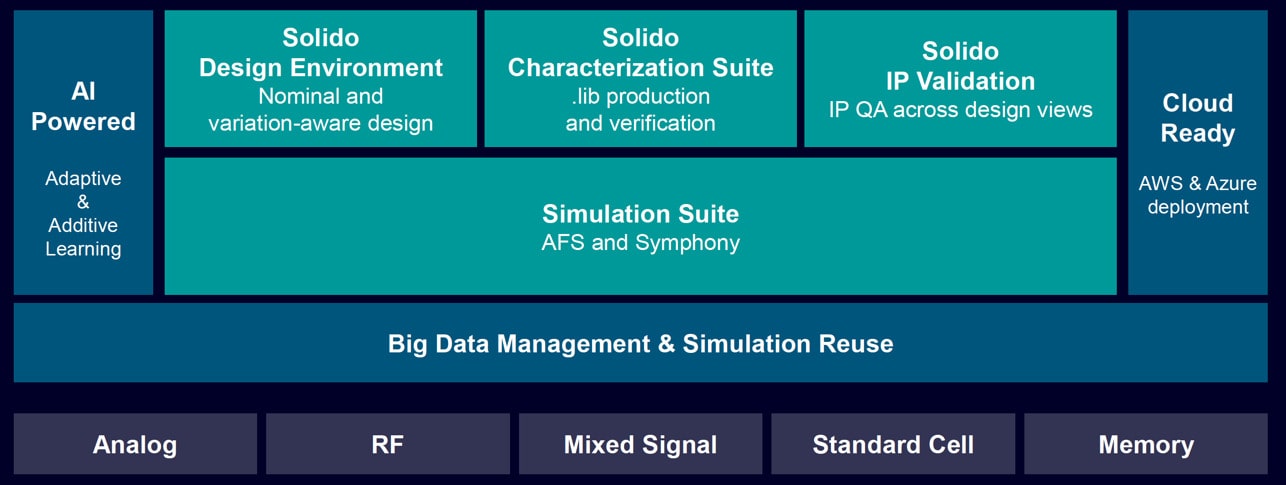

Symphony is a mixed signal simulator that fits into Siemens EDA Custom IC Verification platform consisting of a design environment, characterization suite, and IP validation.

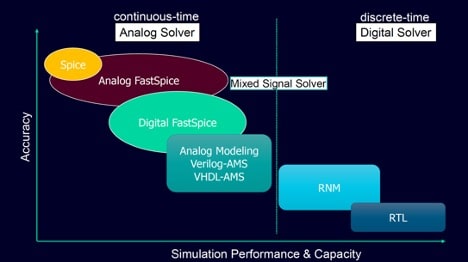

Mixed-signal design accounts for 85% of IC design starts today, per IBS research, and example product categories include: 5G, automotive, AI, HPC, IoT. SPICE circuit simulators provide the highest simulation accuracy at the transistor-level, yet the run times are long. Digital simulators are fast and high capacity, but don’t account for analog. Mixed-signal simulation combines high precision analog blocks with digital blocks, enabling verification.

In mixed-signal verification it’s important to detect top-level connectivity specification errors, find electrical behavior errors, and to ultimately verify that performance metrics were met. Mixed-signal designers want verification tools that have golden SPICE accuracy, are easy to use and setup, enable debug and coverage goals, and that reuse verification infrastructure.

The Symphony platform from Siemens EDA uses AFS XT as the analog solver, is scalable up to 16 cores, supports post-layout simulations, and offers advanced verification and debug. First announced 5 years ago, Symphony continues to grow in popularity with over 100+ customers to date. Symphony benchmarks well versus competitors, showing speed improvements of 2X to 8X for mixed-signal circuits like: HF oscillator, PLL, SerDes, Video TxRx, audio ADC and CMOS image sensors.

All the major foundries have certified the silicon accuracy of AFS across process nodes from 0.5u to 2nm: TSMC, ST, Samsung, Intel, Global Foundries, UMC. Symphony works with digital simulators that model VHDL, Verilog and System Verilog: Questa, VCS, Incisive, Xcelium. Engineers can simulate Symphony using batch mode, command line or interactively with a GUI.

When combing a digital HDL netlist to an analog netlist requires a Boundary Element (BE) for unidirectional or bi-directional connections, and with Symphony the BEs are built-in and can be parameterized, so engineers are not writing any code. Analog signals can be accessed in Verilog or System Verilog modules using analog access functions. Hi-Z states are also detected during mixed-signal simulation.

Simulations with Symphony can have a snapshot taken, then restored for subsequent simulations, saving your team valuable simulation resources. To improve debugging there are features in Symphony to browse all the BEs and even control simulation using Tcl code interactively.

NVIDIA shared at the 2018 Siemens user conference on how they used Symphony to perform mixed-signal verification of a high-speed GPU interface PHY, seeing simulation speed improvements between 2X and 12X from previous tools. Invensense reported that Symphony did noise simulation for a multi-slope ADC with a speedup of 2X to 5X compared to other simulators. Analog Value presented at DVCon 2021 how they did an ADC mixed-mode simulation with Monte Carlo results using 6,590 fewer simulations than brute-force.

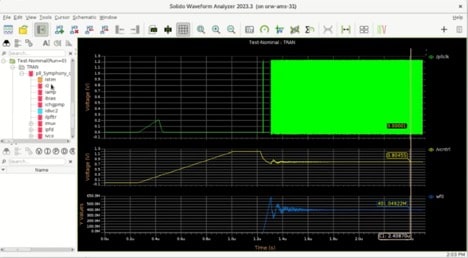

The final part of the webinar was a live demo from Mina Zaki of Siemens EDA, first using the command line with a digital on top netlist, then another example with analog on top. The Solido Waveform Analyzer results were shown for a PLL example.

In the third demo example they showed how BE values could be changed from 2.6V to 1.2V to get the proper simulation results.

Summary

Yes, mixed-signal design and verification is a difficult engineering task, yet with the right tool environment like Symphony and the ability to choose your preferred digital simulator running with AFS, it looks like Siemens EDA has an attractive offer. Their simulation technology is time-tested over the past five years, and has plenty of tier-one adopters, so why not give it a try to improve your mixed-signal turnaround times.

Related Blogs

- Achieving Faster Design Verification Closure

- EDA in the Cloud with Siemens EDA at #59DAC

- New Mixed-Signal Simulation Features from Siemens EDA at DAC

Comments

There are no comments yet.

You must register or log in to view/post comments.