The week before DAC I had the privilege to take a video call with Pradeep Thiagarajan – Product Manager, Simulation, Custom IC Verification at Siemens EDA to get an update on new simulation products. I’ve been following Solido for years now and knew that they were an early adopter of ML for Monte Carlo simulations with SPICE users.… Read More

Tag: afs

Mastering Mixed-Signal Verification with Siemens Symphony Platform

Digital design and verification is well understood by EDA vendors and IC designers, however mixed-signal design and verification is more challenging, because the continuous nature of analog signals requires more compute resources and specialized design skills. Siemens EDA has a unique offering in what they call Symphony… Read More

DAC 2021 – Siemens EDA talks about using the Cloud

My third event at DAC on Monday was all about using EDA tools in the Cloud, and so I listened to Craig Johnson, VP EDA Cloud Solutions, Siemens EDA. Early in the day I heard from Joe Sawicki, Siemens EDA, on the topic of Digitalization.

Why even use the Cloud for EDA? That’s a fair question to ask, and Craig had several high-level… Read More

Electromigration and IR Drop Analysis has a New Entrant

My first IR drop analysis was back in the early 1980s at Intel, where I had to manually model the parasitics of the VDD and VSS interconnect for all of the IO cells that our team was designing in a graphics chip, then I ran that netlist in a SPICE simulator using transient analysis, measuring the bounce in VSS and droop in VDD levels as all… Read More

How About a Faster Fast SPICE? Much Faster!

When Analog FastSPICE was first introduced in 2006 it changed the landscape for high performance SPICE simulation. During the last 14 years it has been used widely to verify advanced nanometer designs. Of course, since then the most advanced designs have progressed significantly, making verification even more difficult. Just… Read More

High Speed SerDes Design and Simulation Webinar Replay from Mentor

Over the years SerDes (serializer/deserializer) based connections have proliferated into just about every connection within and among computing systems. Years ago, parallel interfaces were the most common method of moving data, but issues of signal integrity, synchronization and power simply became too much for the required… Read More

Mentor Adds Circuit Simulators to the Cloud using Azure

Most EDA tools started out running on mainframe computers, then minicomputers, followed by workstations and finally desktop PCs running Linux. If your SoC design team is working on a big chip with over a billion transistors, then your company likely will use a compute farm to distribute some of the more demanding IC jobs over lots… Read More

Device Noise Analysis, What Not to Do for AMS IC Designs

AMS IC designers have a lot to think about when crafting transistor-level designs to meet specifications and schedules, so the most-used tool in their kit is the trusted SPICE or FastSPICE circuit simulator to help analyze timing, power, sensitivity and even device noise. I just did a Google search for “device noise analysis… Read More

Analog Characterization Environment (ACE)

I’m looking forward to the 2013 TSMC Open Innovation Platform Ecosystem Forum to be held Oct. 1[SUP]st[/SUP] in San Jose. One paper in particular that has my attention is titled, “An Efficient and Accurate Sign-Off Simulation Methodology for High-Performance CMOS Image Sensors,” by Berkeley Design Automation & … Read More

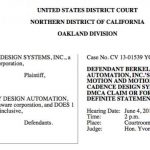

CDNS V. BDA: Motion to Dismiss

The Cadence-BDA saga continues with Berkeley Design Automation today filing a motion to dismiss. You can read the full motion HERE. My previous blog “Cadence Sues Berkeley Design Automation” with 30+ comments is HERE.

The first problem BDA brings up is that the DMCA claim by Cadence is so vague that it doesn’t… Read More