When Analog FastSPICE was first introduced in 2006 it changed the landscape for high performance SPICE simulation. During the last 14 years it has been used widely to verify advanced nanometer designs. Of course, since then the most advanced designs have progressed significantly, making verification even more difficult. Just before DAC I had a conversation with Greg Curtis, Senior Product Manager at Mentor, a Siemens business, about these changes and Mentor’s newest improvements for Analog FastSPICE.

Greg pointed out three main drivers making verification more difficult. He said that the first is increasing interconnect resistance, which is jumping by a factor of 3 at nodes below 16nm. The second is increasing parasitic complexity. With more interconnect coupling and larger interconnect networks, the size of the RC networks is mushrooming. The final driver is new device models with large numbers of model equations – sometimes up to ~600.

While probably every tool during the last 14 years has benefited from improvements in performance, these changes hopefully have been enough to keep up. What designers are really looking for are manifold increases in performance – the kind that are game changing. This is especially true in the world of SPICE simulators, where the number of runs required has increased due to variation at the same time that complexity has increased.

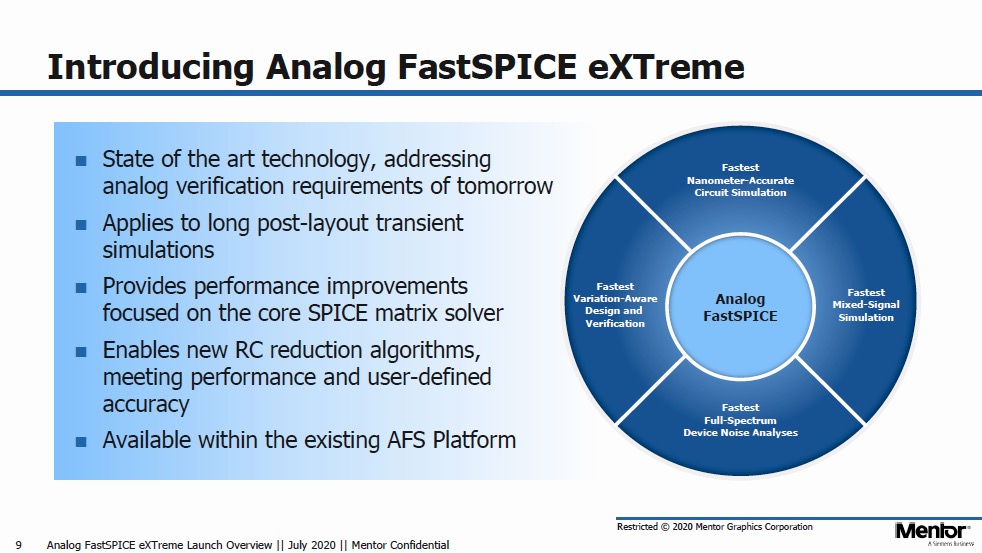

Of course, design teams are used to EDA vendors rolling out new and improved versions of their software, but usually with a hefty price tag for the upgrade. Well, Greg was happy to inform me that on Monday July 20th Mentor is announcing Analog FastSPICE eXTreme with significant performance improvements at no additional cost for existing users. Availability is scheduled for October 2020. OK, but what do you get in this new version?

According to Greg, the focus of the improvements was on post layout simulation. It has become a reality that pre layout simulation is no longer useful, and the first real simulation is with parasitics. Mentor developed a new adaptive core SPICE matrix solver. They also enabled new RC reduction algorithms to help users meet performance and accuracy targets. The RC reduction operates with user-defined accuracy. As before Analog FastSPICE eXTreme will operate in the existing AFS Platform.

Greg had information showing the effectiveness of the speed up in Analog FastSPICE eXTreme. In the case of SRAM timing simulations times there was almost a 4X speed up. For a transceiver they boast a 15X speed up. A quick look at their data shows around an average speed up on various circuit types of 7X. These are impressive numbers.

Mentor was able to cite work with two early adopters on the results achieved with Analog FastSPICE eXTreme. Analog Bits, a leading provider of mixed signal IPs, such as PLLs, Sensors and IOs in processes down to 3nm, spoke of a 6X improvement in simulation times. Silicon Creations, developers of leading edge PLL and SerDes IP, also made comments supporting Analog FastSPICE eXTreme’s improved performance. They saw up to 10X improvement in simulation speed.

It is generally acknowledged that a 10X improvement in any design tool is meaningful in terms of getting users to switch tools. Mentor has taken their well-respected tool and given it that kind of performance improvement. Existing users should be delighted. Users of other tools are going to need to kick the tires simply out of necessity. The full announcement is available for review on the Mentor website. If you are doing SPICE on advanced process nodes, it will be well worth your while.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.