You may have noticed that I have been writing a lot more about analog design lately. This is no accident. Analog and custom blocks are increasingly important because of the critical role they play in enabling many classes of systems, such as automotive, networking, wireless, mobile, cloud, etc. Many of the SoCs needed for these… Read More

Author: Tom Simon

The Path Towards Automation of Analog Design

Power Transistor Modeling for Converter Design

Voltage converters and regulators are a vital part of pretty much every semiconductor-based product. They play an outsized role in mobile devices such as cell phones where there are many subsystems operating at different voltages with different power needs. Many portable devices rely on Lithium Ion batteries whose output voltage… Read More

Benefits of a 2D Network On Chip for FPGAs

The reason people love FPGAs for networking and communications applications is because they offer state of the art high speed interfaces and impressive parallel processing power. The problem is that typically a lot of the FPGA fabric resources are used simply to move the data on or off and across the chip. Achronix has cleverly … Read More

Design to Layout Collaboration Mixed Signal

When talking about today’s sophisticated advanced node designs it’s easy to first think about the digital challenges. Yet, the effort to design the needed analog and mixed signal blocks for them should not be underestimated. The need for high speed clocks, high frequency RF circuits and high bit rate IOs makes the analog portions,… Read More

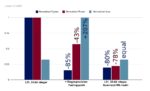

The Importance of Low Power for NAND Flash Storage

Even though we all know that reducing power consumption in NAND Flash Storage is a good idea, it is worthwhile to take a deeper dive into the underlying reasons for this. A white paper by Hyperstone, a leading developer of Flash controllers, discusses these topics providing useful insight into the problem and its solutions. The … Read More

Designing a FinFET Test Chip for Radiation Threats

Much of the technology that goes into aerospace applications is some of the most advanced technology that exists. However, these same systems must also offer the highest level of reliability in what is arguably an extremely difficult environment. For semiconductors a major environmental risk in aerospace applications are … Read More

Path Based UPF Strategies Explained

The development of the Unified Power Format (UPF) was spurred on by the need for explicit ways to enable specification and verification of power management aspects of SoC designs. The origins of UPF date back to its first release in 2007. Prior to that several vendors had their own methods of specifying power management aspects … Read More

Analog Design Acceleration for Chiplet Interface IP

Compared to the automation of digital design, the development of automation for analog has taken a much more arduous path. Over the decades there have been many projects both academic and commercial to accelerate and improve the process for analog design. One of the most interesting efforts in this area is being spearheaded by … Read More

Optimizing AI/ML Operations at the Edge

AI/ML functions are moving to the edge to save power and reduce latency. This enables local processing without the overhead of transmitting large volumes of data over power hungry and slow communication links to servers in the cloud. Of course, the cloud offers high performance and capacity for processing the workloads. Yet, … Read More

Balancing Test Requirements with SOC Security

Typically, there is an existential rift between the on-chip access requirements for test and the need for security in SoCs. Using traditional deterministic scan techniques has meant opening up full read and write access to the flops in a design through the scan chains. Having this kind of access easily defeats the best designed… Read More

Solving the EDA tool fragmentation crisis