Digital design engineers have used DFT automation technologies like scan and ATPG for decades now, however, analog blocks embedded within SoCs have historically required that a test engineer write tests that require specialized expertise and that can take man-months to debug. Siemens has a long history in the DFT field, SPICE… Read More

Tag: ams

Speeding Up Physical Design Verification for AMS Designs

Custom and analog/mixed-signal IC designs have some unique IP and symmetry checking requirements for physical design. Waiting until the end of the IC layout process to verify IP instances for correctness or proper symmetry will cause project delays, so an approach to perform earlier physical verification makes more sense. … Read More

SystemC Update 2024

SystemC version 1.0 came out in 2000 as a C++ class library for system-level modeling and simulation, and on SemiWiki.com there are some 497 references to the language. I wanted to provide an update in this blog so that engineering teams can become more efficient in using SystemC on their SoC projects, saving time and improving product… Read More

Scientific Analog XMODEL #61DAC

Transistor-level circuit designers have long used SPICE for circuit simulation, mostly because it is silicon accurate and helps them to predict the function, timing, power, waveforms, slopes and delays in a cell before fabrication. RTL designers use digital simulators that have a huge capacity but are lacking analog modeling.… Read More

Cadence Debuts Dynamic Duo III with a Basket of Goodies

I am a fan of product releases which bundle together multiple high-value advances. That approach reduces the frequency of releases (no bad thing) in exchange for more to offer per release, better proven through solid partner validation. The Dynamic Duo III release falls in this class, offering improvements in performance, capacity,… Read More

Checking and Fixing Antenna Effects in IC Layouts

IC layouts go through extensive design rule checking to ensure correctness, before being accepted for fabrication at a foundry or IDM. There’s something called the antenna effect that happens during chip manufacturing where plasma-induced damage (PID) can lower the reliability of MOSFET devices. Layout designers run Design… Read More

Mastering Mixed-Signal Verification with Siemens Symphony Platform

Digital design and verification is well understood by EDA vendors and IC designers, however mixed-signal design and verification is more challenging, because the continuous nature of analog signals requires more compute resources and specialized design skills. Siemens EDA has a unique offering in what they call Symphony… Read More

DVCon Europe is Coming Soon. Sign Up Now

I’m a fan of DVCon, a fan of Accellera and a fan of Munich, hosting DVCon Europe once again. This year’s event runs from November 14th through 15th (with some events on the 16th) at the Holiday Inn Munich in the City Center. Phillippe Notton (CEO, SiPearl) will deliver a keynote on “Energy Efficient High-Performance Computing in the… Read More

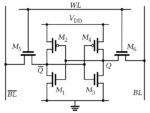

SRAM design analysis and optimization

Every year EDA vendor MunEDA hosts a user group meeting where engineers present how they used automation tools to improve their IC designs, and one presentation from Peter Huber of Infineon caught my attention, it was all about SRAM design optimization. Peter has authored papers at IEEE conferences and been issued patents related… Read More

Accellera Update: CDC, Safety and AMS

I recently had an update from Lu Dai, Chairman of Accellera, also Sr. Director of Engineering at Qualcomm. He’s always a pleasure to talk to, in this instance giving me a capsule summary of status in 3 areas that interested me: CDC, Functional Safety and AMS. I will start with CDC, a new proposed working group in Accellera. To manage… Read More