A recent educational virtual event with the above title was jointly sponsored by Synopsys and Global Foundries. The objective was to bring awareness to state-of-the-art mixed-signal design practices for automotive circuits. The 2-day event comprised of lectures delivered by engineering professors and doctoral students… Read More

Tag: ams

Trust, but verify. How to catch peanut butter engineering before it spreads into your system — Part 2: Verification.

This article about verification is part 2 of a two article series. Please see part 1 on validation HERE.

Verification is a field that has emerged as its own discipline. It’s no longer being relegated to an activity led by the design team to which time is allocated as long as it doesn’t get in the way of designing. Chip companies… Read More

The Tech Week that was January 13-17 2020

In a week where the “phase 1” trade deal between US and China was finally signed, here is all the key news from the semiconductor and technology sector around the world.

After 2 years of an ever increasing trade war, the US and China have signed the so called Phase 1 deal aimed at reducing trade frictions.

Just as important as what is … Read More

Calibre Commences Cloud Computing

Calibre was a big game changer for DRC users when it first came out. Its hierarchical approach dramatically shortened runtimes with the same accuracy as other existing, but slower, flat tools. However, one unsung part of this story was that getting Calibre up and running required minimal effort for users. Two things are required… Read More

Automating Timing Arc Prediction for AMS IP using ML

NVIDIA designs some of the most complex chips for GPU and AI applications these days, with SoCs exceeding 21 billion transistors. They certainly know how to push the limits of all EDA tools, and they have a strong motivation to automate more manual tasks in order to quicken their time to market. I missed their Designer/IP Track Poster… Read More

AMS Experts Share IC Design Stories at #55DAC

At #55DAC in SFO the first day is always the busiest on the exhibit floor, so Monday by lunch time I was hungry and took a short walk to the Marriott hotel nearby to listen to AMS experts from several companies talk about their EDA tool use, hosted by Synopsys:

- Samsung

- Toshiba Memory Corp.

- NVIDIA

- Seagate

- Numem

- Esperanto

Innovation in a Commodity Market

Logic simulation is a victim of its own success. It has been around for at least 40 years, has evolved through multiple language standards and has seen significant advances in performance and major innovations in testbench standards. All that standardization and performance improvement has been great for customers but can present… Read More

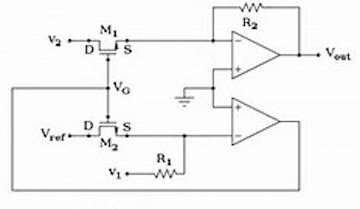

Creative Noise-Reduction in Automotive AMS

Automotive applications are one of the hottest domains today in semiconductor design. We’re bombarded daily with articles on new hybrids, electric cars, ADAS and autonomous cars, trucks and busses. All of these applications are certainly amazing, but the devices that make them work still have to deal with the same old challenges,… Read More

Webinars: Bumper Pack of AMS Webinars from ANSYS

Power integrity and reliability are just as important for AMS designs as they are for digital designs. Ansys is offering a series of five webinars on this topic, under a heading they call ANSYS in ACTION, a bi-weekly demo series from ANSYS in which an application engineer shows you how simulation can address common applications.… Read More

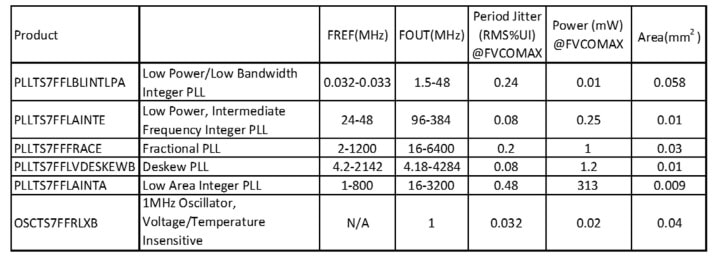

Silicon Creations talks about 7nm IP Verification for AMS Circuits

Designing at 7nm is a big deal because of the costs to make masks and then produce silicon that yields at an acceptable level, and Silicon Creations is one company that has the experience in designing AMS IP like: PLL, Serializer-Deserializer, IOs, Oscillators. Why design at 7nm? Lots of reasons – lower power, higher speeds,… Read More