Remember? During DAC2013 I talked about a new kind of innovation: A Virtual Fabrication Platform, SEMulator3D, developed by COVENTOR. Now, to my pleasant surprise, there is something to report on the proven results from this platform. IBM, in association with COVENTOR, has successfully implemented a 3D Virtual Fabrication methodology to rapidly improve the yield of high performance 22nm SOI CMOS technology.

The CTO-Semiconductor of COVENTOR, Dr. David M. Fried was in attendance while IBM’s Ben Cipriany presented an interesting paper on this work at The International Conference on Simulation of Semiconductor Processes and Devices (SISPAD 2013). The paper is available at the link “IBM, Coventor present 22nm Virtual Fabrication Success at SISPAD” at the COVENTOR website.

Dr. Fried leads COVENTOR’s technology strategy, partnerships and external relationships. His expertise touches upon areas such as Silicon-on-Insulator (SOI), FinFETs, memory scaling, strained silicon, and process variability. He is a well-respected technologist in the semiconductor industry, with 45 patents to his credit and a notable 14-year career with IBM, where his latest position was “22nm Chief Technologist” for IBM’s Systems and Technology Group.

I had a nice opportunity speaking to Dr. Fried on phone during the conference at Glasgow, Scotland. From the conversation, all I can say is that SEMulator3D really has a true innovation and fascinating technology that will majorly ease the complex design and manufacturing process, not only at 22nm but still lower nodes in the days to come; specifically in analyzing and predicting the key phenomenon of variability at these nodes, quickly and accurately.

The Conversation –

Q: I guess the first introduction of SEMulator3D in wide public media was in DAC 2013?

Actually COVENTOR is a 17 years old company, with experience in MEMS s/w, Device simulation and Design enabling tools. It has many years of 3D structural modelling experience from the MEMS field, which has been migrated over the last 7 years into the Semiconductor space after encouragement by Intel, one of our original investors. I moved to COVENTOR about a year ago, and am now driving its technology roadmap and expanding SEMulator3D usage across the semiconductor industry. In 2012, we made a very important updated release of SEMulator3D. But in 2013, our newest release, developed in significant collaboration with IBM, adds lots of automation, advanced modelling and really takes a quantum leap forward in virtual fabrication.

Q: This is a new concept of Virtual Fabrication Platform. How does it relate with the design flow at Fabless companies?

It provides a flexible process platform for Fabless companies to explore the physical embodiment of their specific design IPs, otherwise they do not know what happens at the process end. In other words, it is a “Window into the Fab” for Fabless companies. Variability mainly depends on physical parameters. Because SEMulator3D is 10-100 times faster than other process modelling tools, it can provide many more data points of physics-driven highly predictive and accurate models, giving a more rigorous view of the variability effects.

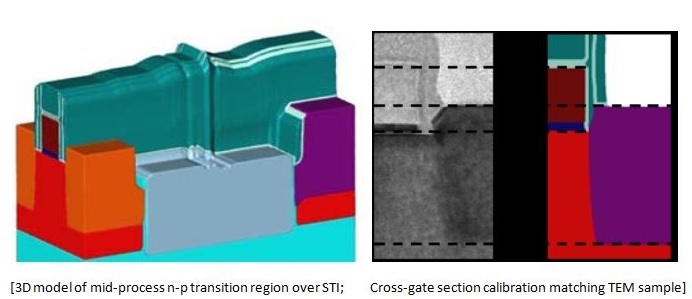

Q: Let’s see some of the aspects of this paper presented at SISPAD. It’s a meticulous work that the 3D model was matched to inline measurement and metrology data as well as 2D SEM/TEM cross-section images of a nominal transistor. How did you get this idea to model this way, so accurately?

In any modelling situation, first of all, we need to gain faith by experimenting with the past results and demonstrating the perfect match with the existing data, calibrate and then predict. The modelling engine is physics-driven, so it will correctly predict many processes and effects without any calibration. For this detailed study, the nominal model was validated against a significant amount of inline measurement and metrology, and also TEMs and SEMs and iterations of calibration were performed. After that, thousands of cases of variation were performed and the results were assembled and analysed quantitatively. SEMulator3D 2013 adds the first production availability of our Expeditor tool which enables automated spreadsheet-based process variation study and analysis. Our expanded Virtual Metrology capabilities can automatically collect and analyse the structure during the minutes of modelling rather than the months these experiments could spend in the fab.

Q: It is observed that major process variation occurs at the n-p interface due to spatial exposure and overlay errors from multiple lithography levels whose edges define that interface. So, how difficult it is when multiple devices in a large layout are involved?

Right, the nfet-pfet interface is used in this work as a vehicle for the study and can easily be scaled to larger design space. Expeditorenables massively parallel execution, so the same type of modelling can be applied to many different design elements, such as cells in a design library. That’s how there is really no comparison between SEMulator3D and any TCAD tool out there. SEMulator3D is extremely fast, applicable to a larger physical design space and provides yield focused modelling.

Q: How large a design, SEMulator3D can handle to model and evaluate for process window tolerance?

There is effectively no limitation on design area. What matters is modelling time. SEMulator3D can do the typical job in minutes rather than weeks. The concept is to choose the smallest area of a design which can be modelled to solve a specific process integration challenge, apply process description and define resolution of models. And then parallelize the job. Some users are investigating large memory arrays, some users are investigating single transistor effects. Most of our typical users are applying this modelling platform at the circuit-scale.

Q: So, how do you choose that smallest sample, process description and resolution?

In our more collaborative engagements, like the one in this paper, we work with the customer to define these aspects and optimize the modelling exercise. The customer is always interested in their specific design IP, but we can help optimize the area selection and parallelization. The process description is where we do most of our collaboration. Each customer’s process is different, and developed independently, but we spend time working with “Modelling Best Known Methods” and many tricks of the trade we’ve learned in virtual fabrication. The modelling resolution is flexible based on the effects being studied and can be tailored to optimize modelling performance based on the granularity of the effects being analysed.

Q: What kind of different design structures have been modelled using SEMulator3D?

There are many, to name a few – DRAM, SRAM, logic, Flash memory, ESD circuitry, Analog circuits, TSVs, multi-wafer 3D integration structures, and so on.

Q: We know IBM is already working closely with COVENTOR. Who are the other customers using SEMulator3D?

Our primary user base is in the Foundries, IDMs and Memory manufacturers. We are engaged with the top 9 worldwide semiconductor manufacturers and also several Fabless design houses. With Cadencewe have provided a Virtuoso Layout Editor link to SEMulator3D. SEMulator3D also has its own full-function layout editor which serves as a conduit to any existing GDSII.

Q: One last question. Although, from this conversation, what I can perceive is that this tool has a bright future which can provide a solid foundation to designs at ultra sub-micron process nodes, I would like to know your view on what’s in store for future?

One of the things I spend a lot of time thinking about is 3D DRC. You know, most yield limitations come from a physical problem that is 3D in nature. That single 3D problem gets exploded into 100s of 2D rules to provide a DRC checking infrastructure. In many cases, it’s becoming cumbersome and inefficient to do it this way, especially in the development phase where these rules are just being explored. That’s an area to work on and optimize by doing 3D searches on structural models. There are some structures that will be better checked in 3D rather than with a massive set of translated 2D rules. So, in the future 3D Design Rule Checking will be a reality, and we are working hard on that.

This was a very exciting and passionate conversation with Dr. Fried, where I could enhance my knowledge about process modelling. And, I can see that SEMulator3D can provide competitive advantage to design companies as well, because this facilitates their parallel interaction with Fab in a virtual world which can be used to mitigate the manufacturing related issues at the design stage. A novel concept!

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.