The transition from FinFET to Gate-All-Around (GAA) transistor technology represents a pivotal moment in the evolution of logic devices, driven by both physical scaling limits and the rapidly growing computational demands of artificial intelligence. As semiconductor technology approaches the sub-3 nm regime, traditional… Read More

Tag: finfet

Accelerating IC Design: Silvaco’s Jivaro Parasitic Reduction Tool

In Silvaco’s July 2025 video presentation at the 62nd Design Automation Conference (DAC), Senior Staff Applications Engineer Tim Colton introduced Jivaro, a specialized parasitic reduction tool designed to tackle the escalating challenges of post-layout simulation in advanced IC designs. As semiconductor nodes… Read More

Alchip’s Technology and Global Talent Strategy Deliver Record Growth

Alchip Technologies Ltd., a global leader in high-performance computing (HPC) and artificial intelligence (AI) ASIC design and production services, continues its trajectory of rapid growth and technical leadership by pushing the boundaries of advanced-node silicon, expanding its global design capabilities, and building… Read More

An Invited Talk at IEDM: Intel’s Mr. Transistor Presents The Incredible Shrinking Transistor – Shattering Perceived Barriers and Forging Ahead

IEDM turned 70 last week. This was cause for much celebration in the form of special events. One such event was a special invited paper on Tuesday afternoon from Intel’s Tahir Ghani, or Mr. Transistor as he is known. Tahir has been driving innovation at Intel for a very long time. He is an eyewitness to the incredible impact of the Moore’s… Read More

The TSMC OIP Backstory

This is the 15th anniversary of the TSMC Open Innovation Platform (OIP). The OIP Ecosystem Forum will kick off on September 27th in Santa Clara, California and continue around the world for the next two months in person and on-line in North America, Europe, China, Japan, Taiwan, and Israel. These are THE most attended semiconductor… Read More

Gate Resistance in IC design flow

MOSFET gate resistance is a very important parameter, determining many characteristics of MOSFETs and CMOS circuits, such as:

• Switching speed

• RC delay

• Fmax – maximum frequency of oscillations

• Gate (thermal) noise

• Series resistance and quality factor in MOS capacitors and varactors

• Switching speed and uniformity… Read More

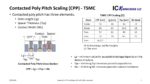

IEDM 2022 – TSMC 3nm

TSMC presented two papers on 3nm at the 2022 IEDM; “Critical Process features Enabling Aggressive Contacted Gate Pitch Scaling for 3nm CMOS Technology and Beyond” and “A 3nm CMOS FinFlexTM Platform Technology with Enhanced Power Efficiency and Performance for Mobile SOC and High Performance Computing Applications”.

When … Read More

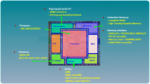

Achieving 400W Thermal Envelope for AI Datacenter SoCs

Successful ASIC providers offer top-notch infrastructure and methodologies that can accommodate varied demands from a multitude of customers. Such ASIC providers also need access to best-in-class IP portfolio, advanced packaging and test capabilities, and heterogeneous chiplet integration capability among other things.… Read More

Samsung Versus TSMC Update 2022

After attending the TSMC and Samsung foundry conferences I wanted to share some quick opinions about the foundry business. Nothing earth shattering but interesting just the same. Both conferences were well attended. If we are not back to the pre pandemic numbers we are very close to it.

TSMC and Samsung both acknowledged that there… Read More

3D Device Technology Development

The VLSI Symposium on Technology and Circuits provides a deep dive on recent technical advances, as well as a view into the research efforts that will be transitioning to production in the near future. In a short course presentation at the Symposium, Marko Radosavljevic, from the Components Research group at Intel, provided … Read More