You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The TSMC Technical Symposium is today so I wanted to give you a brief summary of what was presented. Tom Dillinger will do a more technical review as he has done in the past. I don’t want to steal his thunder but here is what I think are the key takeaways. First a brief history lesson.

The history of TSMC Technology Development with 12 key… Read More

Much of the technology that goes into aerospace applications is some of the most advanced technology that exists. However, these same systems must also offer the highest level of reliability in what is arguably an extremely difficult environment. For semiconductors a major environmental risk in aerospace applications are … Read More

Intel recently released an exceptional video providing an insightful chronology of MOS transistor technology. Evolution of Transistor Innovation is a five-minute audiovisual adventure, spanning 50 years of Moore’s Law. Some of the highlights are summarized below, with a few screen shot captures – the full video is definitely… Read More

Last Thursday Intel held their investors meeting, in this write up I wanted to focus on my areas of coverage/expertise, process technology and manufacturing.

Technology Development presented by Ann Kelleher

Last year Intel presented their Intel Accelerated plan and, in this meeting, we got a review of where Intel stands on that… Read More

It Isn’t Transistory

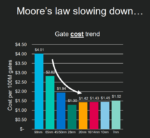

There’s a quiet upheaval happening in the semiconductor industry. The rules that have always governed the industry are fraying, undoing assumptions that we took for granted, that was pounded into us in school. The irreproachable Moore’s Law, that exponential progress will make things cheaper, better,… Read More

While the trend towards System-on-Chip (SoC) has been gathering momentum for quite some time, the primary driver has been integration of digital components, spurred by Moore’s law. Integrating more and more digital circuitry into a single chip has been consistently beneficial for performance, power, form factor and economic… Read More

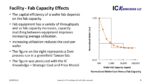

I was invited to give a plenary address at the SISPAD conference in September 2021. For anyone not familiar with SISPAD it is a premiere TCAD conference. This year for the first time SISPAD wanted to address cost and my talk was “Cost Simulations to Enable PPAC Aware Technology Development”.

For many years the standard in technology… Read More

Humans certainly have always had an aesthetic preference for symmetry. We also see symmetry showing up frequently in nature. The importance of symmetry in electronic designs has been apparent for decades. There are a host of analog structures that require balanced layout. For instance, these include differential pairs and … Read More

The annual VLSI Symposium provides unique insights into R&D innovations in both circuits and technology. Indeed, the papers presented are divided into two main tracks – Circuits and Technology. In addition, the symposium offers workshops, forums, and short courses, providing a breadth of additional information.

At… Read More

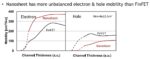

At the 2021 Symposium on VLSI Technology and Circuits in June a short course was held on “Advanced Process and Devices Technology Toward 2nm-CMOS and Emerging Memory”. In this article I will review the first two presentations covering leading edge logic devices. The two presentations are complementary and provide and excellent… Read More