They say what adds value is to take something difficult and make it look simple. USB looks so simple when it is done right, but designers know it can be one of the more tempermental features in an SoC, especially in the latest SuperSpeed incarnation.

We were having some vigorous conversation recently on the new paradigm of SoC design flow moving in the direction of software. Our own Daniel Payne chimed in with an anecdote that indicates there is room for improvement in USB designs:

“I agree, software compatibility is key to success. As an example I just bought a $35.00 Linux-based single-board computer called the Raspberry Pi, however after playing with it have discovered that the USB ports don’t always work with my Logitech wireless mouse and keyboard, forcing me to un-plug and re-connect, not real friendly or viable. The SoC is from Broadcom and I suspect it’s a software driver issue with the modified version of Debian Linux.”

The key to that statement is “… don’t always work.” In most minds that symptom implicates the host driver, since things work after hardware reset. In the SoC world, with data flying between functional blocks all over the place, problems like this aren’t exactly separable. This is the relatively new science of co-verification: making sure hardware and software don’t just work, but stay working under all conditions of things happening around them in real-time.

This problem is by no means unique to USB. It exists for any fast serial interface with bi-directional protocols: Ethernet, PCI Express, MIPI, HDMI, and others. Three things conspire to make SuperSpeed USB a particularly difficult challenge: speed, distance, and variety.

Speed is a wonderful thing, until the SoC designer is faced with the problem of having to put all the data coming in somewhere, reliably. USB 2.0 wasn’t all that fast at 480Mbps, but the increase in USB 3.0 to the SuperSpeed mode of a theoretical 5Gbps can bring in a lot of data very quickly. Are there enough buckets to carry several hundred megabytes of data a second while there are other things going on in the SoC?

Distance is interesting. The USB spec allows a cable up to 5m (16 ft). Being tech literate, you probably have quite a few USB gadgets in your reach. Here’s a test: do you have any that are connected with a 5m cable? Have you ever even seen a 5m USB cable? Why is that? There are two problems inside this one: signal integrity, and IR drop. Both are lesser issues with shorter cables, but there’s always the what if – and it often gets blamed on the cable.

Variety may be the spice of life, but it’s the salt of interoperability wounds. The very nature of the ‘U’ in USB means people expect it to work with anything plugged into it. That means a USB protocol stack in an SoC from vendor A has to work in all conditions with the USB protocol stack in a target device from vendor B. Have vendor A and vendor B ever talked to each other? In a PC world, the answer is probably, but in the embedded world, the answer is maybe. Embedded USB stacks are optimized for footprint size and ported to real-time operating systems.

At some point, if you design with SuperSpeed USB, you are very likely to get in over your head. The solution for a $35 hobbyist platform is unplug/replug, but the solution for a tablet or a piece of medical diagnostic equipment or an infotainment system in a car is: test and verify IP before it gets out there, in the early stages of SoC design.

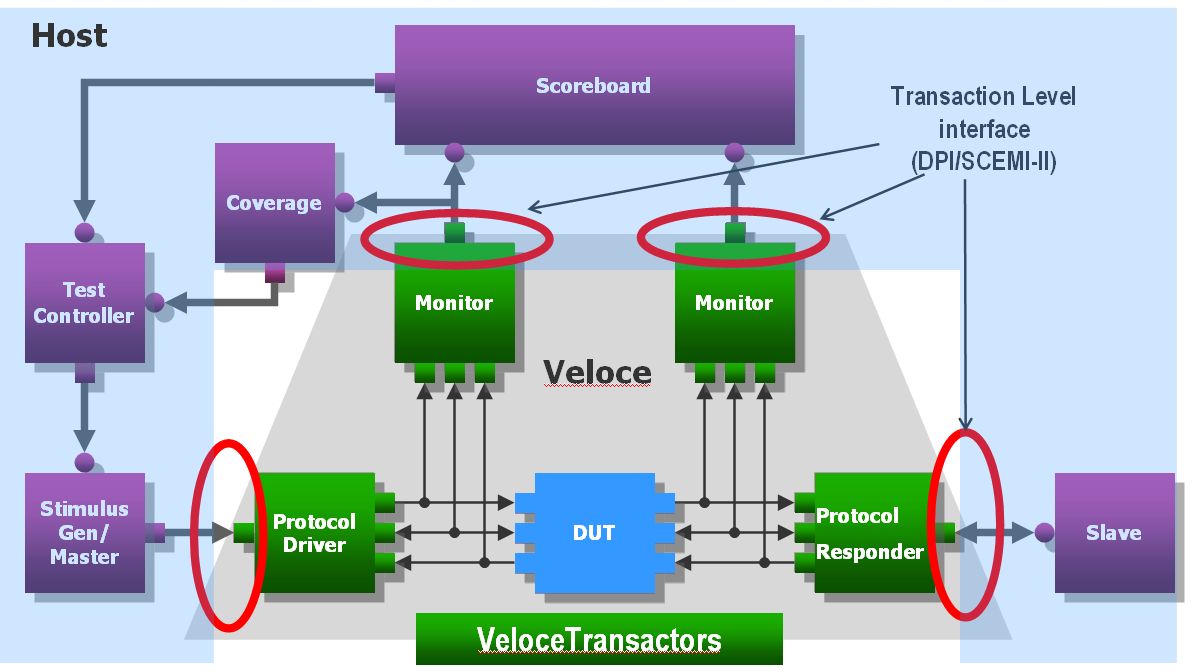

There are platforms that provide visibility inside an SoC, and there are platforms that verify USB protocols – and now they’ve come together to aid in IP co-verification. Mentor Graphics and Teledyne LeCroy have teamed the Veloce Emulation System and the Voyager M3i protocol verification platform. As we’ve discussed, virtual platforms are good for functional IP verification, but to really troubleshoot IP integration issues something better is needed. The answer doesn’t have to be maybe when an SoC can be emulated.

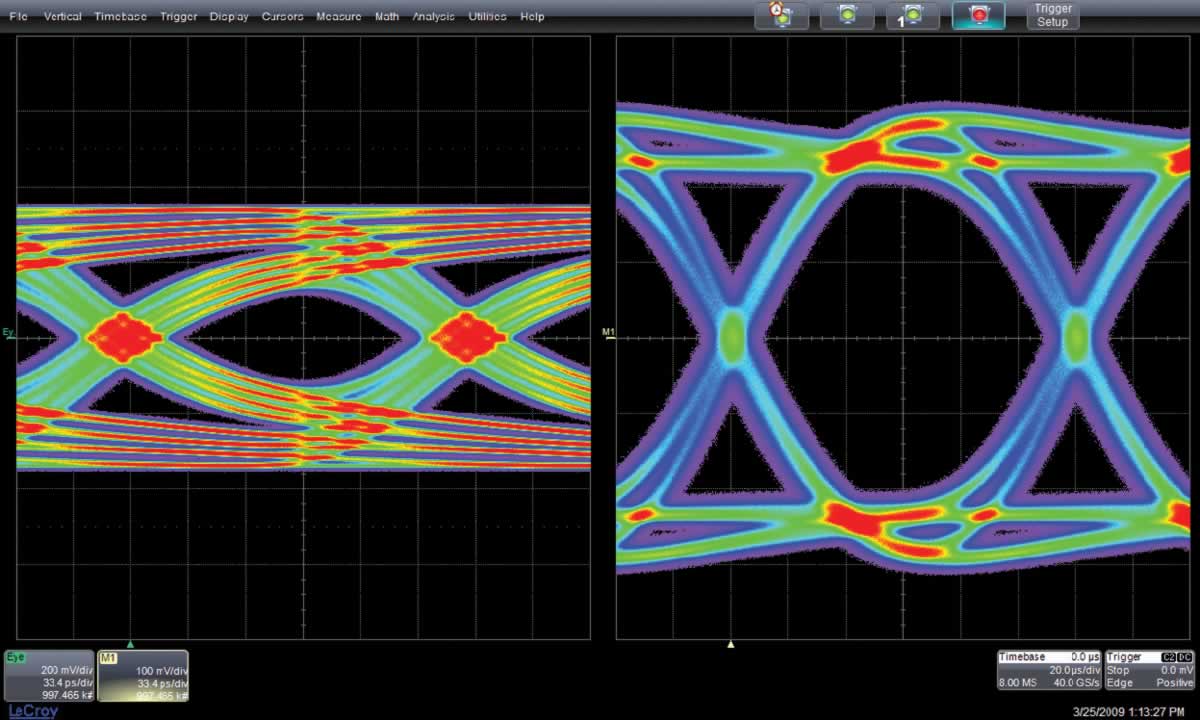

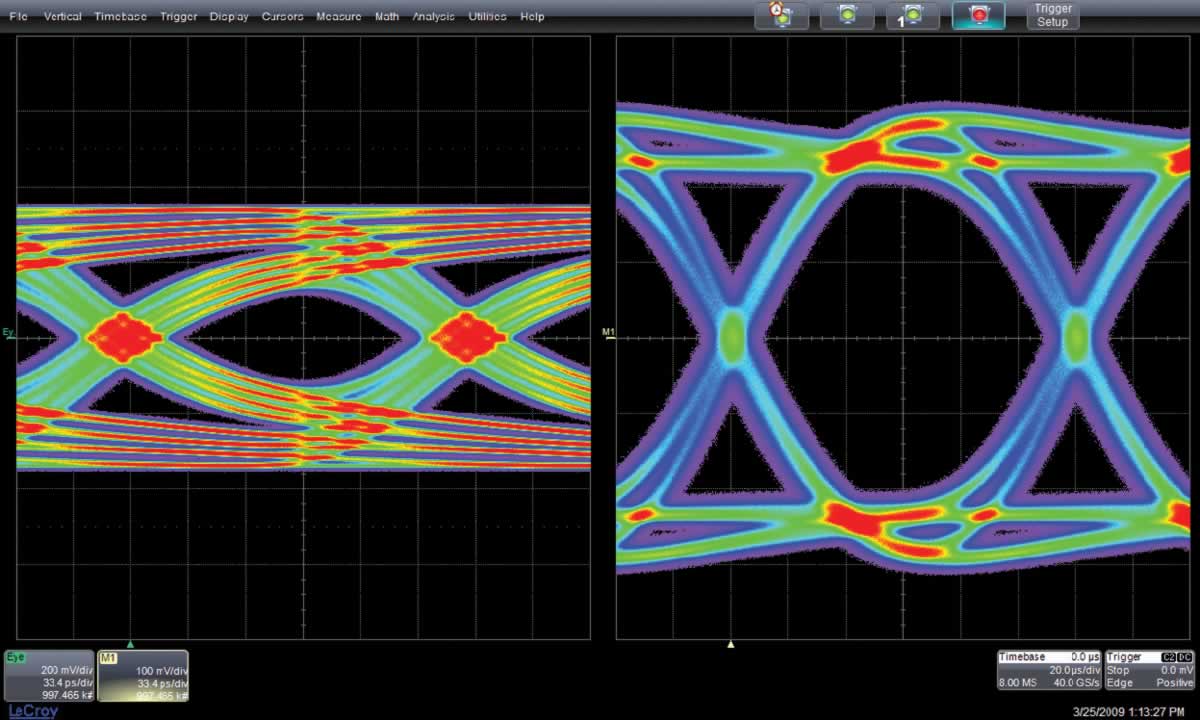

According to Mike Micheletti, product manager for USB protocol verification tools at Teledyne LeCroy, the pairing of the Voyager M3i brings its advanced USB link stimulus and traffic scenario capability to bear. With a full USB 3.0 compliance package behind a link exerciser, the Voyager M3i can analyze SuperSpeed links at their rated speed.

While the Mentor Veloce emulation system is really fast – 50 to 10,000 times faster than simulation solutions according to Mentor – SuperSpeed links require adaptation to match up with the Veloce system emulation speed. Teledyne LeCroy has added a feature to the Voyager M3i to provide that adaptation: what they call an ultra-slow clock (at least in the context of 5Gbps), ranging from 350kHz to 12.5MHz. This allows syncing of an external reference clock from the Veloce to the Voyager M3i, providing clock-by-clock patterns from the exerciser at the right speed. That means instead of trying to guess exactly where a lengthy USB pattern fired at the SoC under emulation went wrong, the Veloce scoreboards the complete SoC state at each point in sync with the USB stimulus, and the Voyager M3i tools can also be brought to bear.

Mentor has a similar teaming arrangement for baseband chip testing with Rohde & Schwarz, using the CMW500 LTE protocol tester and other equipment. Mentor’s term for this is hardware assisted pre-silicon testing.

This type of teaming, bringing in protocol instrumentation experts and their world-class instruments in partnerships to help verify high-speed interface IP and how it integrates into an SoC design, is something we’re likely to see more of in EDA solutions.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.