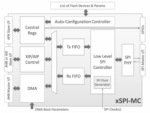

SPI, invented some four decades ago, is so successful as a low-pin-count interface for microcontrollers and processor cores that it spurred memory makers to incorporate both the physical signaling interface and advanced memory command protocols into serial flash and serial pseudo-SRAM (PSRAM) devices. Those protocols, … Read More

Author: Don Dingee

Configurable xSPI memory controller IP core is FuSa-ready

WEBINAR: Intrinsic Techniques in RF Power Amplifier Design

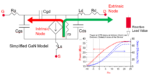

Load-pull power amplifier (PA) design techniques determine the optimal impedances at the power transistor’s extrinsic reference plane, which is the physically accessible boundary for measurement or simulation. This reference plane can be the package transistor leads, die bond pads, or IC chip terminals. It includes… Read More

Securing UALink in AI clusters with UALinkSec-compliant IP

A classic networking problem is securing connections with encrypted data, but implementing strong encryption algorithms at wire speeds can limit performance. However, introducing blazing-fast connectivity without an encryption strategy leaves systems vulnerable. The architects in the UALink Consortium, including … Read More

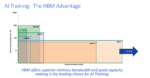

WEBINAR: HBM4E Advances Bandwidth Performance for AI Training

The rapid proliferation of LLMs and other AI applications, and of high-end GPU platforms that run them, is putting intense pressure on the performance requirements for memory technologies. Designers need to be keenly aware of how to make the most of their memory and controller choices, which can be moving targets given the rapid… Read More

WEBINAR: Two-Part Series on RF Power Amplifier Design

At lower frequencies with simpler modulation, RF power amplifier (PA) designers could safely concentrate on a few primary metrics – like gain and bandwidth – and rely on relaxed margins to ensure proper operation in a range of conditions. Today’s advanced RF PA design is a different story. mmWave and sub-THz frequencies introduce… Read More

On the high-speed digital design frontier with Keysight’s Hee-Soo Lee

High-speed digital (HSD) design is one of the more exciting areas in EDA right now, with design practices, tools, and workflows evolving to keep pace with increasing design complexity. With the annual Chiplet Summit and DesignCon festivities right around the corner, we sat down with Keysight’s Hee-Soo Lee, HSD Segment Lead, … Read More

WEBINAR: What It Really Takes to Build a Future-Proof AI Architecture?

Keeping up with competitors in many computing applications today means incorporating AI capability. At the edge, where devices are smaller and consume less power, the option of using software-powered GPU architectures becomes unviable due to size, power consumption, and cooling constraints. Purpose-built AI inference … Read More

Sophisticated soundscapes usher in cache-coherent multicore DSP

Digital audio processing is evolving into an art form, particularly in high-end applications such as automotive, cinema, and home theater. Innovation is moving beyond spatial audio technologies to concepts such as environmental correction and spatial confinement. These sophisticated soundscapes are driving a sudden increase… Read More

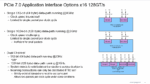

WEBINAR: PCIe 7.0? Understanding Why Now Is the Time to Transition

PCIe is familiar to legions of PC users as a high-performance enabler for expansion slots, especially GPU-based graphics cards and M.2 SSDs. It connects higher-bandwidth networking adapters and niche applications like system expansion chassis in server environments. Each PCIe specification generation has provided a leap… Read More

Webinar: RF board design flow examples for co-simulating active circuits

In part one of this webinar series, Keysight and Modelithics looked at the use of 3D passive vendor component models supporting highly accurate, automated 3D EM-circuit co-simulation of high-frequency RF board designs. Part two continues the exploration of RF board design flows for simulating active circuits on boards, again… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!