For a while it seemed like Mentor lived on the margins of the (RTL) design-for-power game. They had interesting  micro-architectural optimization capabilities through their Calypto heritage but no real industry chops in power estimation, a must-have when you are claiming to reduce power. Better known offerings in RTL power estimation have dominated the landscape: PowerArtist, SpyGlass Power and more recently Joules.

micro-architectural optimization capabilities through their Calypto heritage but no real industry chops in power estimation, a must-have when you are claiming to reduce power. Better known offerings in RTL power estimation have dominated the landscape: PowerArtist, SpyGlass Power and more recently Joules.

(A quick sidebar to head off complaints from the emulation guys – there are excellent solutions for power estimation built around emulation. But that’s not what you need when you’re tweaking microarchitecture on a block; block designers most commonly use simulation to generate activity files.)

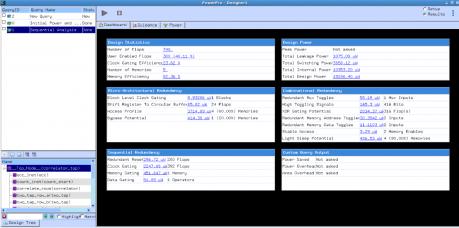

It now looks like Mentor has stepped up to the big table with their PowerPro solution. They have power estimation that looks comparable to the Cadence and Synopsys solutions (with one caveat) and they have further strengthened their tools for finding opportunities for optimization and (if you choose) implementing and verifying those changes automatically.

Accuracy in estimation is important first because you only want to implement proposed changes that give a big saving so you want to be sure the tool is in the ballpark when ranking candidates, and second because you don’t want your picks to wind up increasing power because implementation realities weren’t considered.

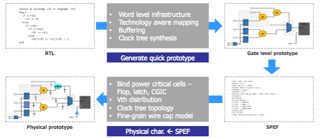

A large part of the art of getting this (reasonably) right is in acceptably modeling how the design will be physically synthesized. You want to do realistic tech mapping, ensure that datapath elements will map to efficient design macros, you want to synthesize a reasonable clock tree with reasonable buffering, you want to guide from UPF (or estimate) reasonable Vth distributions and you absolutely must fold in realistic physical data – wire lengths, clock tree topology and so on.

PowerPro seems to be covering most of these bases, at least to the extent Mentor are willing to share details. They use SPEF to import physical information, a realistic choice given the range of possible physical platforms. The downside is that this lacks tight coupling with physical design which might allow for further optimization. But there’s a potential upside for IP developers – you don’t want to tie optimization choices to just one implementation. Comparison between a few different implementations could be a good way to guide optimization for more general use.

In any case, tool vendors need to be careful not to over-engineer RTL power estimation. Mentor claims ~15% accuracy to gate-level based on their own correlation studies. This is exactly what everyone else claims. You may have read my comments elsewhere that these things are in a distribution. Perhaps 1σ is at 15%, but all solutions show outliers and it’s not clear any vendor has cracked making the distribution any tighter, so PowerPro seems to be right in the middle of the pack.

Next we get to an area where PowerPro may lead the pack – micro-architectural power optimization. This always starts by assuming first-order clock or memory enable gating constraints (or logic) has been correctly defined by the designer. Tools then look for what additional gating could be inserted to save power. These methods are formal, looking upstream and downstream of first-order gates for what additional constraints (or strengthening of existing constraints) those constraints logically imply. These cases can add up. I have heard of potential for up to 15% further saving, a large chunk of that coming especially from memory-gating.

Through Calypto functionality, Mentor is able to look many clock cycles forward and backwards in logic to find opportunities. Since looking this deep could generate an overwhelming number of suggested improvements, PowerPro does a cost-benefit tradeoff analysis, comparing power, area and timing to filter out just those suggestions that look optimal. A number of the power saving techniques are quite familiar – looking for redundant reads and writes on a memory for example. Some techniques sounded innovative (at least to me):

- Redundant reset checks, for flops in a design which are not directly observable (like many low power suggestions, making this fix may not be a good idea for other reasons. But in some cases it might)

- PowerPro is able to find logic for memory enable and light sleep pins – no need for labeling on your part

- PowerPro will look for sequential data gating opportunities, eg an expensive operation like multiply in cases when the output is don’t care

All changes are formally-verified to be functionally equivalent, using Calypto’s well-proven SLEC.

There’s a nice interface for selecting fixes you want to implement, also to explore other power reduction options (reducing voltage in some areas for example), supported by macros that let you explore pre-canned options like DVFS.

PowerPro supports (user-controlled) automatic implementation of selected fixes in the RTL. A few years ago, I remember auto-fixing being looked on with deep disdain by most RTL designers (no tool is going to mess with my RTL). But it seems that’s changing; Mentor said they now see a 50-50 split. I guess that was going to come at some point; I’m just surprised how quickly the user-base is switching.

You might wonder why I opened this blog with a picture of cupcakes. Mentor served these at the lunch and learn. I was told they are very healthy, gluten-free and they were certainly attractive and tasty. Not so sure about the healthy part.

Overall, PowerPro looks like a pretty complete RTL estimation and optimization solution. You can learn more about the product HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.