As semiconductor technology advances and nodes continue to shrink, designers are faced with increasing challenges related to device complexity, power consumption, and reliability. The delicate balance between high performance, low power usage, and long-term reliability is more critical than ever. This growing demand … Read More

Tag: power reduction

Checking Clock Gating Equivalence the Easy Way

Synopsys just delivered a Webinar on using the sequential equivalence app (SEQ) in their VC Formal product to check that clock-gating didn’t mess up the functional intent of your RTL. This webinar is one in a series on VC Formal, designed to highlight the wide range of capabilities Synopsys has to offer in formal verification. They… Read More

A Credible Player at the Power Table

For a while it seemed like Mentor lived on the margins of the (RTL) design-for-power game. They had interesting micro-architectural optimization capabilities through their Calypto heritage but no real industry chops in power estimation, a must-have when you are claiming to reduce power. Better known offerings in RTL power … Read More

A Comprehensive Power Optimization Solution

In an electronic world driven by smaller devices packed with larger functions, power becomes a critical factor to manage. With power consumption leading to heat dissipation issues, reliability of the device can be affected, if not controlled or the device not cooled. Moreover, for mobile devices such as smartphones or tablets… Read More

A Tool Conceived With Designers’ Input and Developed from Scratch

If we look at the past, most of the EDA tools in the semiconductor design space have originated from a designers’ need to do things faster. Regardless of whether it is design exploration, manual design, simulation, verification, optimization (Power Performance Area – PPA) and many other steps in the overall design flow.… Read More

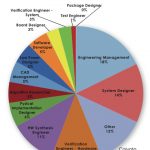

Calypto 2013 Report

Each year Calypto runs a survey of end-users. This year’s survey and report has two parts, power reduction and high level synthesis (HLS).

The topics covered are:

- survey methodology and demographics

- top methods used to reduce power

- engineering time spent on specfiic RTL tasks to reduce power

- plans to deploy RTL power reduction

Reducing Dynamic and Static Power in Memories

Sequential approaches to power reduction work well on logic implemented using standard cells. But part of every SoC, sometimes a very large part, is taken up with embedded memories for which alternative approaches are required. Not only do these memories occupy up to half of the area they also account for as much as 75% of the power… Read More