You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Are you ready for the premier conference for functional design and verification of electronic systems?

Sponsored by Accellera Systems Initiative, DVCon is an independent, not-for-profit organization dedicated to creating design and verification standards required by systems, semiconductor, intellectual property (IP)… Read More

Switching translates to power. Similar to the recent slow down experienced by Moore’s Law, the constant power density (power demand per unit chip area) prescribed by Dennard scaling was no longer affordable across the technological scaling. While the contribution of leakage power component in advanced process nodes was getting… Read More

Some of the world’s most complex Systems-on-Chip (SoCs) are being developed for automotive applications. These SoCs have heterogeneous architectures with a variety of processors and accelerators that do real-time image processing for assisted and autonomous driving applications. The Bosch Visiontec team, in Sophia Antipolis,… Read More

ARM has become such a worldwide powerhouse in delivering processors to the semiconductor IP market because they have done so many things well: IP licensing model, variety, performance, and low-power. On my desk are two devices with ARM IP, a Samsung Galaxy Note 4 smart phone and a Google tablet. Most of my readers will likely have… Read More

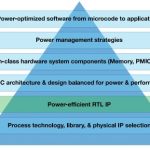

There was a comment recently that design for low power is not an event, it’s a process; that comment is absolutely correct. Power is affected by everything in the electronic ecosystem, from application software all the way down to layout and process choices. Yet power as a metric is much more challenging to model and control than … Read More

There are a lot of clever techniques to automatically find and even implement methods for register gating and memory gating, but the bulk of power-saving still depends on designer and architect insight based on expected range of use of a device, complemented by practical use-case simulations. Of course this team needs to be able… Read More

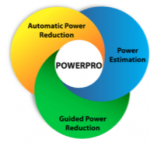

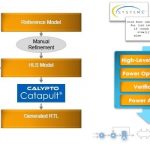

For a while it seemed like Mentor lived on the margins of the (RTL) design-for-power game. They had interesting micro-architectural optimization capabilities through their Calypto heritage but no real industry chops in power estimation, a must-have when you are claiming to reduce power. Better known offerings in RTL power … Read More

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More

For about a decade I am looking forward to seeing more of system level design and verification including high level synthesis (HLS), virtual prototyping, and system modeling etc. to come in the main stream of SoC design. Although the progress has been slow, I see it accelerating as more and more tools address the typical pain points… Read More