PCI Express 3.0 specification is 1000 pages long. Most of us, and most of the designers integrating PCIe gen-3 into their latest ASIC, FPGA or system will probably never read it completely, or even open it. In fact, they don’t need to read it completely, but they should care about one point, whether they buy an ASSP or a PCIe design IP: is this precise IP being certified? For the IP vendor, this certification can be obtained by submitting the freshly designed PCIe IP to a “Plug Fest”, or interoperability program organized by PCI Special Interest Group (PCI-SIG). Because PCI Express is defined as an Interface Protocol, the PCIe agent, Root Port (the equivalent of the Host in USB) or Endpoint (the Device equivalent), is supposed to be interfaced with any PCIe agent, Device or a Root Port respectively, not necessarily coming from the same design source, IP vendor or ASSP chip maker. During the Certification program, your PCIe IP will be plugged in front of various systems being used as reference, like Motherboards, and will have to pass a pre-defined operation test list. For an IP vendor, obtaining the PCI-SIG certification is the first step for successful market introduction, especially if you sale PCI Express Design IP.

Synopsys has just announced that their PCI Express® 3.0 is the first complete solution from a single vendor to pass compliance testing at the first PCI-SIG compliance workshop for PCI Express 3.0. According with Synopsys, this means that “to achieve compliance, the DesignWare PHY and controller IP passed PCI-SIG’s three required Gold Tests: the electrical tests, the Protocol Test Card (PTC) and the PCIeCV software tests. In addition, the DesignWare PHY and controller IP demonstrated interoperability with more than 80 percent of the devices at the workshop, exceeding interoperability requirements.” For Synopsys customer being in the decision process for sourcing the PCIe PHY, Controller or Verification IP, knowing that these IP has obtained certification will dramatically increase the level of confidence into the product, and ease taking the decision. But not only, as the PCI-SIG certification is “associative” (think about your old algebra lesson!), the chip integrating this Design IP will be certified as well!

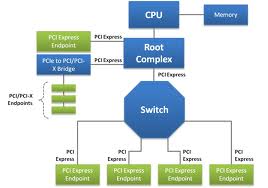

Let me tell you a short story about plug fest. When PCI Express gen-1, the very first specification, has been issued in 2004, the market was still using PCI or PCI-X, both being parallel based interface protocol. PCIe gen-1 has introduced the bidirectional, dual simplex concept, supported by a SerDes based PHY, and the Controller was also based on something new in the PC space, the layered based protocol, including the Media Access Layer (MAC), the Transmission Link Layer (TLL) and the Application Layer (AL). Nevertheless, the PCI-SIG had to organize the very first plug-fest, as demonstrating interoperability was crucial to start a successful market introduction campaign.

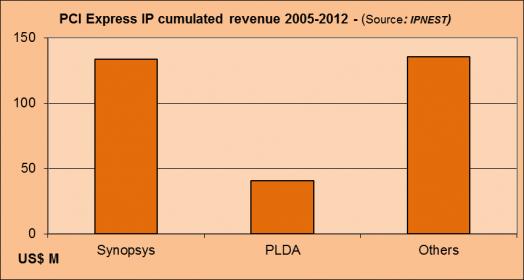

Guess who had designed the PCI Express Controller to be used as a reference? A small IP vendor named Cascade… that Synopsys bought almost immediately, ringing the start of a very successful PCIe IP sale decade, as you can see on the graphic below, as Synopsys has made almost $150 million in PCIe IP sales since Cascade acquisition. But if you read Semiwiki, you have seen this post and already know this story.

Remark: this graphic has been extracted from the “PCIe IP Survey”, very recently updated by IPnest (the very last buyer is a well-known FPGA vendor, who has integrated SerDes supporting PCIe very early… and continue to do so!).

Eric Esteve from IPNEST

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.