As the complexity of modern System-on-Chip (SoC) designs continues to rise, achieving energy efficiency measured as performance per watt has become a crucial design goal. With the increasing demand for powerful, multifunctional chips, balancing performance with power consumption has become essential. Realistic workloads and advanced power analysis methods are vital for modern SoC design to help engineers improve energy efficiency early in the development process.

Traditional power analysis methods use synthetic simulation vectors to estimate SoC power consumption. These vectors, designed to mimic potential workloads, often miss the dynamic and unpredictable nature of real-world scenarios, resulting in significant lack of accuracy of power analysis. Often, designs that appear efficient in simulations may consume more power in actual use, leading to inefficient optimization efforts.

To address these limitations, incorporating software-driven workloads during power analysis is essential. Such realistic workloads provide an accurate representation of real-life applications, capturing nuances of power consumption that synthetic vectors miss. By emulating actual operating conditions, engineers can identify genuine power consumption bugs and optimize designs for better energy efficiency.

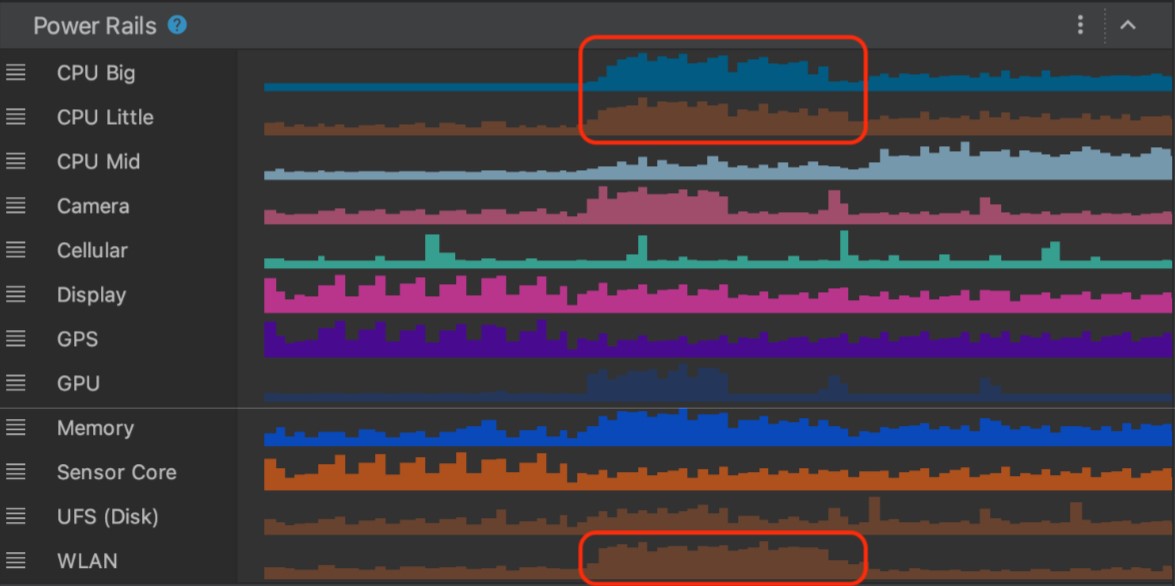

Advanced power analysis methods, such as using an emulation environment coupled with passively parallel power analysis, enable continuous monitoring and analysis of power consumption across multiple scenarios. This approach captures detailed power consumption data for real system operation, identifying patterns and anomalies that indicate inefficiencies. Such methods offer a true assessment of SoC power consumption, ensuring optimization efforts are based on accurate and relevant information.

One key benefit of using realistic workloads and advanced power analysis methods is the ability to ‘shift-left’ in the design process. Shifting left allows designers to address potential issues and optimizing designs earlier in the development cycle, preventing costly redesigns and ensuring the final product meets energy efficiency goals.

As the demand for powerful and efficient SoCs grows, traditional power analysis methods are no longer sufficient. Realistic workloads and advanced power analysis techniques offer a more accurate and comprehensive assessment of power consumption, enabling effective optimization. By shifting left and addressing energy efficiency early in development, companies can create competitive products that meet market demands.

Join our upcoming webinar on July 16 to learn more about these innovative approaches and enhance your SoC design’s energy efficiency. Register now to stay ahead of the rapidly evolving field of SoC design.

New Webinar: Making it Real: How to Use Realistic Workload Scenarios to Enhance Energy Efficiency in SoC Designs

Tue, Jul 16, 2024 10:00 AM – 11:00 AM PDT

Abstract:

As complexity of modern SoC designs is continuing to increase, energy efficiency – or performance per watt – has emerged as one of the primary design goals. Traditional methods of power analysis use synthetic simulation vectors – which may not represent real use cases. This approach may result in under-estimating power consumption, failing to detect real wasted power conditions, and guiding optimization efforts in the wrong direction. In this webinar, you will learn how using realistic workloads in the emulation environment, coupled with a passively parallel power analysis capability, provides a true assessment of the SoC power consumption, and enables you to have confidence to ‘shift-left’ to improve the energy efficiency of your design.

Speaker Bio:

William Ruby is the senior director of product management for Synopsys Power Analysis products. He has extensive experience in the area of low-power IC design and design methodology and has held senior engineering and product marketing positions with Cadence, ANSYS, Intel, and Siemens. William holds MBA, MSEE, and physics degrees, and has been awarded a patent in high-speed cache memory design.

Also Read:

Synopsys-AMD Webinar: Advancing 3DIC Design Through Next-Generation Solutions

Reduce Risk, Ensure Compliance: Hardware-Assisted Verification for Design Certification

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.