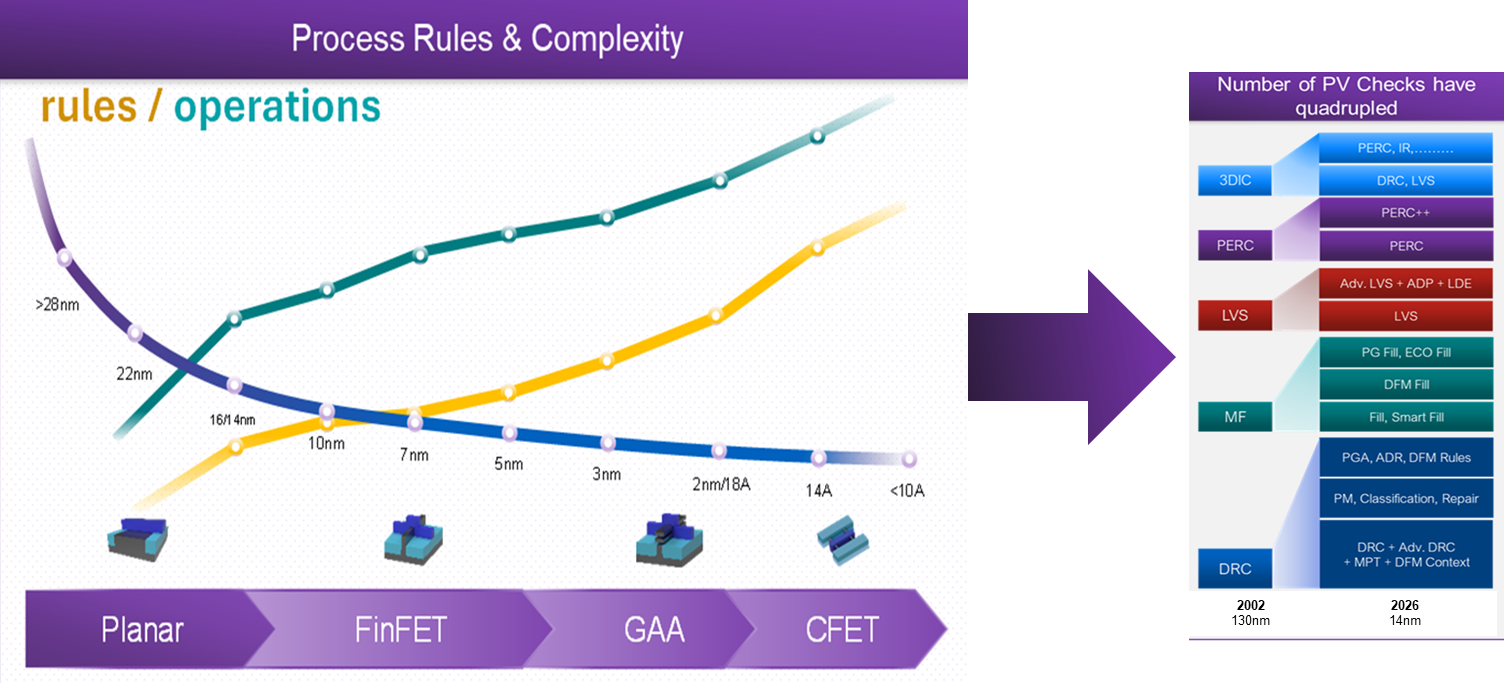

It is well-known that advanced semiconductor process technology presents substantial challenges across the full design flow and global supply chain. In this piece, we will focus on a particularly difficult problem – physical verification. This design step is the final gate to manufacturing. Producing a final tape‑out GDS that complies with all foundry signoff rules is required to ensure functional silicon. As process nodes shrink, the explosion of rules and operations is substantial. And the expanded interaction of subtle effects has also caused the required number of checks to quadruple.

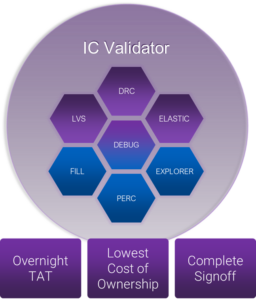

This problem represents a discontinuity in the design flow. The traditional and trusted methods of yesterday do not scale to address these new requirements. Conquering these requirements demands a modern software architecture and innovative methodologies. In this post we’ll explore the dimensions and challenges of physical verification and highlight a new approach that tames these issues. The graphic at the top of the post illustrates a high-level view of what design teams are facing. Let’s examine the problem in more detail and explore an effective solution as we explain how to overcome the advanced node physical verification bottleneck.

The Problem

Physical verification is an unforgiving task. Thanks to the expanded use of digital and analog chiplets integrated with advanced packaging technology, designs must pass 100% of all checks across the digital, analog and packaging flows. A partial list of these checks includes DRC, LVS, FILL, PERC/ESD, Antenna, and Stress.

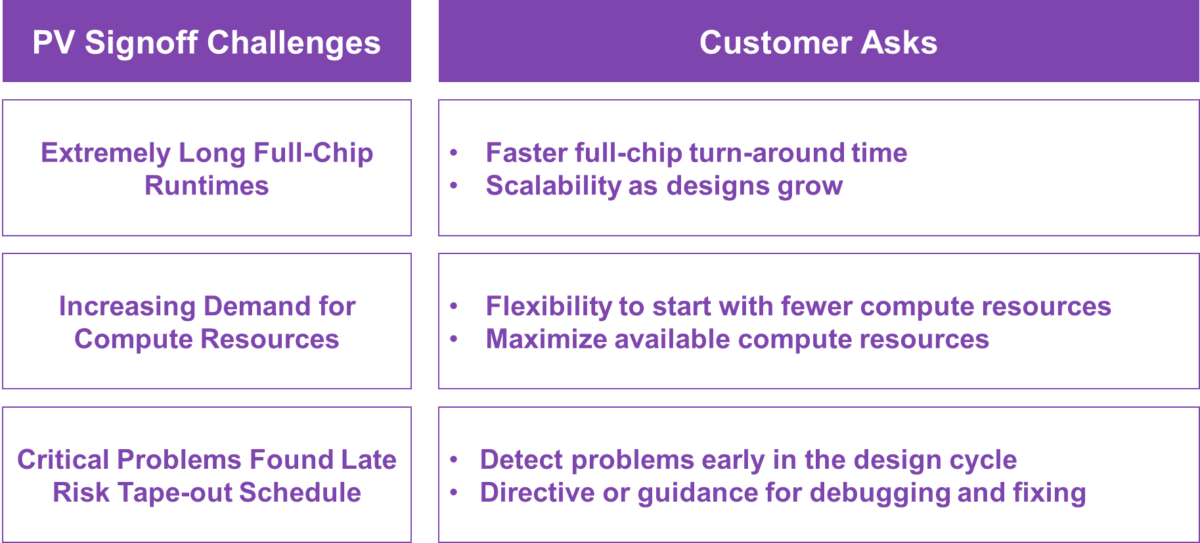

The actual list is much longer. For many of these checks, complexity and run time are increasing exponentially. Full-chip runs often require days to weeks to complete. And sometimes those long runs don’t finish at all. The figure below summarizes a few of the critical bottlenecks design teams are facing.

Beyond the specific number and complexity of tasks now involved in physical verification, there is a common thread in the table presented above – the ability to use compute resources in a flexible, elastic way. An approach like this will reduce overall cost and improve efficiency. More on this in a moment.

To highlight the size of the physical verification problem, here are a couple of facts about the various bottlenecks design teams face:

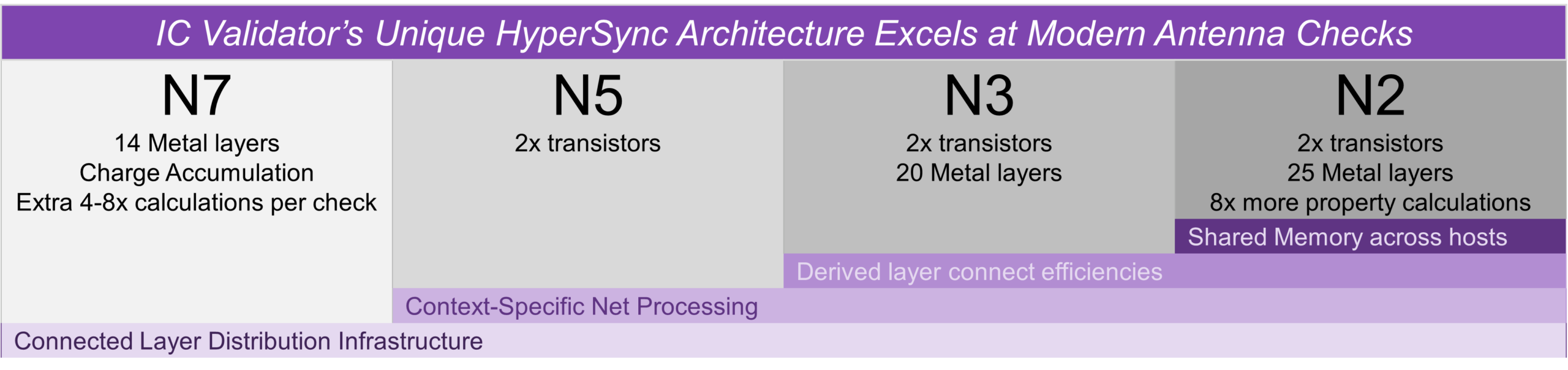

- Full-chip antenna checks: Between N7 and N2 there has been an 8X increase in transistor count. Metal layers have grown from 14 to 25. And there are now 8x more property calculations.

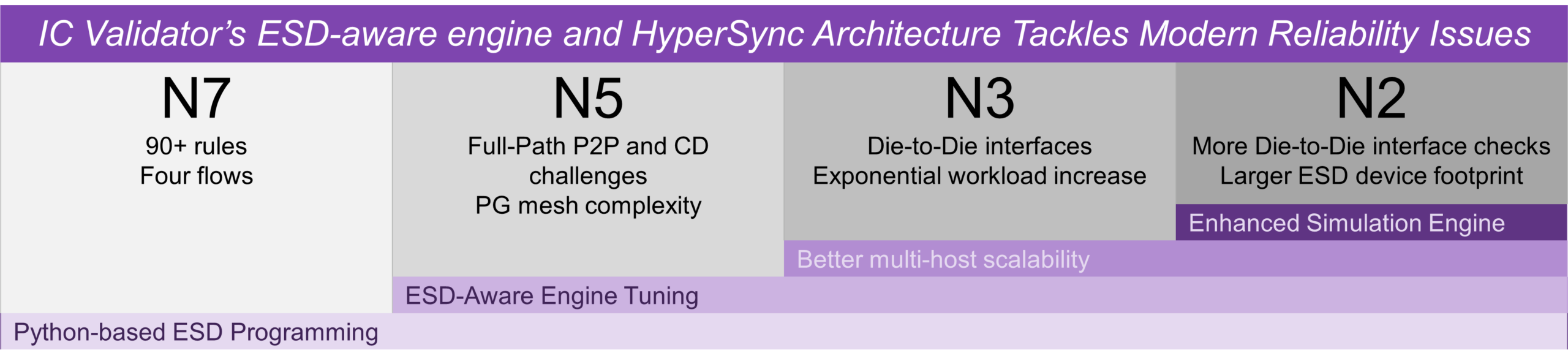

- Full-chip PERC ESD checks: These checks typically take weeks to complete. This impacts ESD verification and fixing, putting the tape-out schedule at risk. At N2, there are many more die-to-die interface checks and a larger ESD device footprint.

The Solution – Synopsys IC Validator

Synopsys IC Validator represents a fresh approach to physical verification, reinforcing its commitment to performance and excellence in this domain, delivering the industry’s best distributed processing scalability. Its performance and scalability have enabled some of the industry’s largest reticle limit chips with billions of transistors, same day design rule checking (DRC), antenna rule checking, layout versus schematic (LVS), and programmable electrical rule checking (PERC) turn-around time.

Solving a problem this large requires a broad design flow footprint. IC Validator seamlessly integrates with the Synopsys Fusion Compiler™ RTL-to- GDSII solution, 3DIC Compiler, the IC Compiler® II place and route system, Custom Compiler, and StarRC for golden signoff parasitic extraction. This integrated physical verification solution handles the challenges presented by hyper convergent chip design. That is, multiple technologies, architectures, and protocols integrated into a single, complex semiconductor design.

The Fusion Technology delivered by IC Validator accelerates design closure for manufacturing by enabling independent signoff-quality analysis and automatic repair within a unified implementation environment. Let’s look a bit closer at a couple of the more difficult checks and how IC Validator removes barriers.

Full-Chip Antenna Checks

Antenna complexity is increasing exponentially, resulting in full-chip antenna runs becoming a major bottleneck for tape-outs. The IC Validator HyperSync architecture enables (or improves) connectivity and antenna scaling to help overcome these challenges. Across many design styles, including hyperscaler, network processor, CPU/GPU and complex ASICs, IC Validator delivers 2X – 4X faster turn-around time. And often CPU core usage is reduced by 70% compared to traditional, legacy approaches.

The diagram to the right illustrates how well the tool’s performance scales for full-chip antenna checks. And the diagram below illustrates the impact of IC Validator’s unique HyperSync architecture as process nodes advance.

Full-Chip PERC ESD Checks

To provide a bit of background, programmable electrical rules checking (PERC) is a method for assessing chip reliability issues that cannot be checked with DRC or LVS. These reliability checks are frequently electrostatic discharge (ESD) related, but they can extend to other areas as well, including electrical overstress and dielectric breakdown. The rules involve connectivity and netlist information but also need to support full customization from design to design making the process challenging.

Full-path PERC ESD runs often take weeks to complete, significantly impacting ESD verification and fixing and risking the tape-out schedule. IC Validator’s HyperSync architecture helps to tackle flat ESD problems with intelligent scaling. Across designs including complex ASICs, CPU/GPUs, mobile and CPU processors IC Validator delivers 2X – 4X faster turn-around time for full-chip PERC ESD. In some cases, the product successfully completed the run when other tools could not.

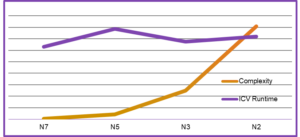

The diagram to the right illustrates how well the tool’s performance scales for full-chip PERC ESD checks. And the diagram below illustrates the impact of IC Validator’s unique ESD-aware engine and HyperSync architecture as process nodes advance.

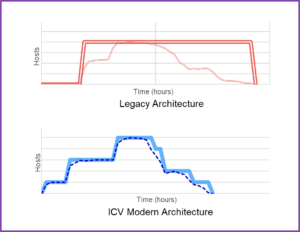

Optimal Compute Efficiency with Elastic Compute

As mentioned above, the ability to use compute resources in a flexible, elastic way is a critical element to taming advanced node physical verification bottlenecks. IC Validator’s architecture supports highly efficient, massive-scale distributed processing, dynamically utilizing CPU cores during runs without affecting overall turn-around time. This reduces compute cost with 50% less hardware resources. This approach eliminates queue time and optimizes resource utilization without turn-around-time impact. The system is highly optimized for both cloud and on-premises environmentsand eliminates the need for a customized deck-splitting approach to achieve target turn-around times.

The bottom line is that design teams can get the best runtime with 50% less compute resources for large SoC designs. The figure on the right illustrates the effectiveness of this architecture when compared with traditional, legacy approaches.

Early Exploration and In-Design Flows

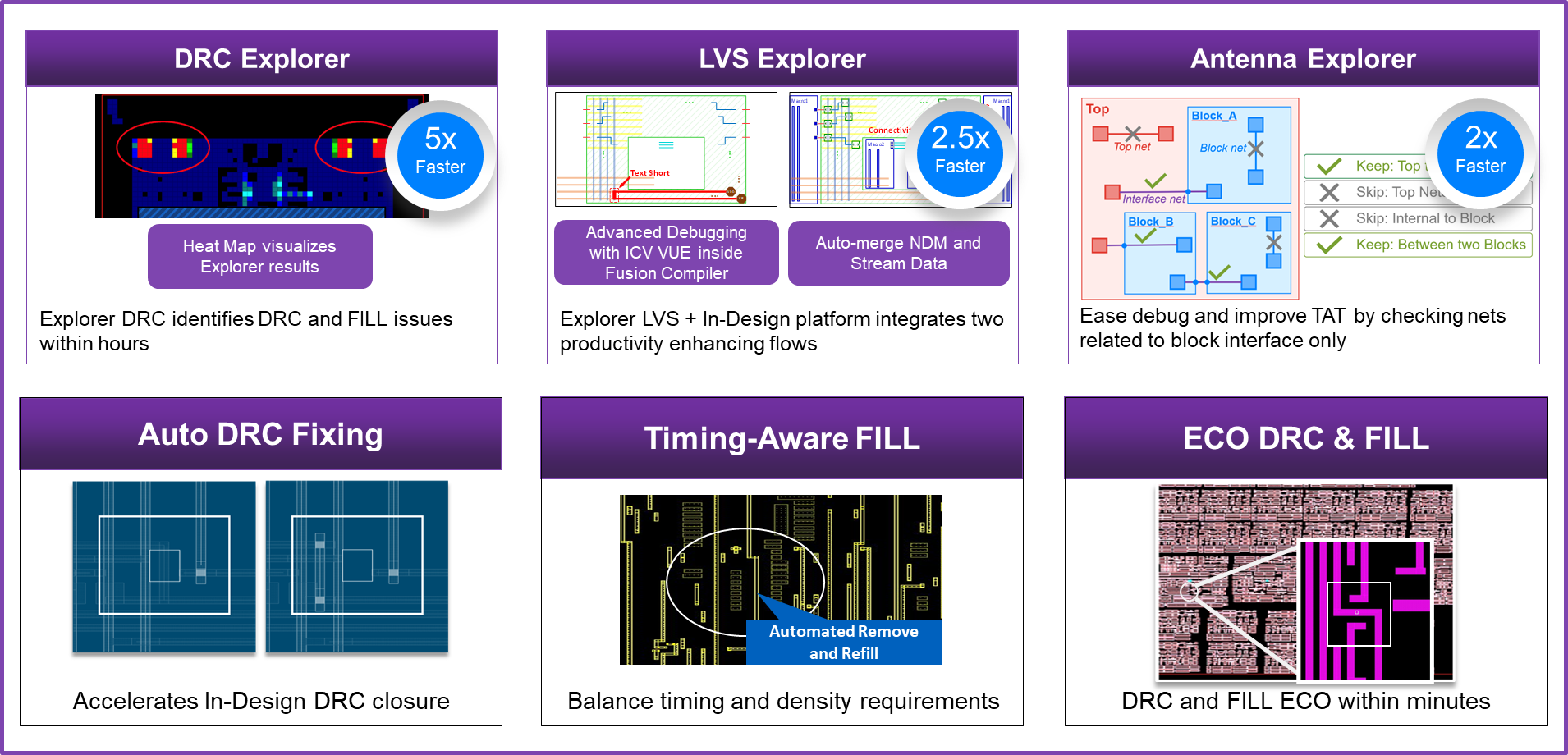

To get to tape-out on time requires review and fixing of errors across many checks. Each one presents its own unique set of challenges and requirements. Thanks to the broad set of In-Design flows that are part of IC Validator, this process becomes more coherent, consistent and efficient. The figure below shows a view of the tools available.

DRC Explorer uses advanced technology and signoff foundry decks to find the most important design problems quickly on dirty designs, using fewer resources while achieving faster runtimes.

LVS Explorer is similar, focusing on fast checks of top-level shorts and opens, avoiding complicated LVS debug efforts that complicate signoff.

Antenna Explorer allows the user to focus on the most common cause of antenna violations: those that occur at the interfaces between top level routing and IP blocks. By eliminating unnecessary and irrelevant violations, designers clean interface antenna issues efficiently.

Automatic DRC fixing leverages the signoff quality of IC Validator results against the efficiency of the Fusion Compiler router. This integrated flow cuts down on painful manual iterations between the two tools.

Similarly, timing-aware fill is able to identify timing critical nets and provide adequate spacing to foundry fill shapes, thus performing the necessary metal fill step while maintaining the timing closure status.

When DRC checking and metal fill are done in the In-Design environment, incremental updates are possible after manual modifications to the layout by the user. DRC checks become lightning fast, and metal fill is inserted surgically, minimizing the impact to parasitics, timing, and signal integrity.

Customer Adoption and Foundry Certification

IC Validator adoption in the market is accelerating with industry-leading customers leveraging its full-chip performance and hardware efficiency for signoff applications.

IC Validator is certified by leading foundries across advanced process nodes, with qualified runsets available directly from the foundries.

To Learn More

We have touched on some of the significant challenges to tape-out an advanced node design. A new approach to tape-out is required to meet these challenges, time-tested traditional approaches can no longer be relied upon.

IC Validator offers a modern, fully unified approach that delivers results for comprehensive physical verification sign-off for advanced designs. We’ve discussed how its HyperSync architecture enables massive scalability for full-chip PERC ESD and antenna checks. With Elastic Compute, IC Validator reduces compute cost with 50% less compute resources. And thanks to early exploration and In-Design applications using foundry-certified runsets, design convergence is accelerated.

IC Validator offers a modern, fully unified approach that delivers results for comprehensive physical verification sign-off for advanced designs. We’ve discussed how its HyperSync architecture enables massive scalability for full-chip PERC ESD and antenna checks. With Elastic Compute, IC Validator reduces compute cost with 50% less compute resources. And thanks to early exploration and In-Design applications using foundry-certified runsets, design convergence is accelerated.

In future posts, we will share results from top-tier customers who are using IC Validator to tape-out some of the world’s most sophisticated designs. Until then, you can learn more about Synopsys IC Validator here or contact Synopsys if you have any questions. And that’s how to overcome the advanced node physical verification bottleneck.

Also Read:

Podcast EP342: The Evolution and Impact of Physical AI with Hezi Saar

WEBINAR: Beyond Moore’s Law and The Future of Semiconductor Manufacturing Intelligence

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.