As the new name reflects, chip and system design were a major focus at DAC. So was the role of AI to enable those activities. But getting an AI-enabled design flow to work effectively across chip, subsystem and system-level design presents many significant challenges. One important one is effectively managing the vast amount of… Read More

Author: Mike Gianfagna

Perforce at DAC, Unifying Software and Silicon Across the Ecosystem

Arteris Simplifies Design Reuse with Magillem Packaging

Many know Arteris as the “network-on-chip”, or NoC, company. Through acquisitions and forward-looking development, the footprint for Arteris has grown beyond smart interconnect IP. At DAC this year, Arteris highlighted its latest expansion with a new SoC integration automation product called Magillem Packaging. The announcement… Read More

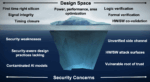

Caspia Focuses Security Requirements at DAC

As expected, security was a big topic at DAC this year. The growth of AI has demanded complex, purpose-built semiconductors to run ever-increasing workloads. AI has helped to design those complex chips more efficiently and with less power demands. There was a lot of discussion on these topics. But there is another part of this trend.… Read More

Webinar – Power is the New Performance: Scaling Power & Performance for Next Generation SoCs

What if you could reduce power and extend chip lifetime, without compromising performance? We all know the importance of power optimization for advanced SoCs. Thanks to the massive build out of AI workloads, power consumption has gone from a cost or cooling headache to an existential threat to the planet, if current power consumptions… Read More

Visualizing System Design with Samtec’s Picture Search

If you’ve spent a lot of time in the chip or EDA business, “design” typically means chip design. These days it means heterogeneous multi-chip design. If you’ve spent time developing end products, “design” has a much broader meaning. Chips, subsystems, chassis and product packaging are in focus. This is just a short list if you consider… Read More

DAC News – A New Era of Electronic Design Begins with Siemens EDA AI

AI is the centerpiece of DAC this year. How to design chips to bring AI algorithms to life, how to prevent AI from hacking those chips, and of course how to use AI to design AI chips. In this latter category, there were many presentations, product announcements and demonstrations. I was impressed by many of them. But an important observation… Read More

Caspia Technologies at the 2025 Design Automation Conference #62DAC

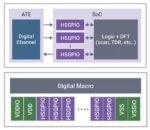

Security will be an important topic at DAC this year. The hardware root of trust is the foundation of all security for complex systems implementing AI workloads. Thanks to new and sophisticated techniques the hardware root of trust is now vulnerable and must be protected. But adding deep security verification to existing design… Read More

Synopsys Addresses the Test Barrier for Heterogeneous Integration

The trend is clear, AI and HPC is moving to chiplet-based, or heterogenous design to achieve the highest levels of performance, while traditional monolithic system-on-chip (SoC) designs struggle to scale. What is also clear is the road to this new design style is not a smooth one. There are many challenges to overcome. Some are … Read More

Infinisim Enables a Path to Greater Profitability and a Competitive Edge

Improved profitability and competitiveness are at the very heart of every enterprise. Achievements like this are usually attributed to corporate culture. Sometimes, it’s just being in the right place at the right time. Some organizations make huge investments with top-tier consulting companies to help find their way.

Recently… Read More

The Road to Innovation with Synopsys 224G PHY IP From Silicon to Scale: Synopsys 224G PHY Enables Next Gen Scaling Networks

The explosive growth of large language models (LLMs) has created substantial new requirements for chip-to-chip interconnects. These very large models are trained in high-performance data centers. Multiple accelerators need to work seamlessly to make all this possible as the bandwidth between accelerators directly impacts… Read More

Moore’s Law Wiki