A recent announcement from Synopsys signals a meaningful escalation in the race to build next-generation AI hardware. The expanded collaboration between Synopsys and TSMC brings together silicon-proven IP, AI-driven design tools, and cutting-edge manufacturing processes in a tightly integrated effort to accelerate high-performance computing (HPC) and AI system development. More than a routine partnership update, the move reflects a broader industry transition toward ecosystem-level innovation, where success depends on how well design, IP, and fabrication technologies align from the outset.

What Was Announced

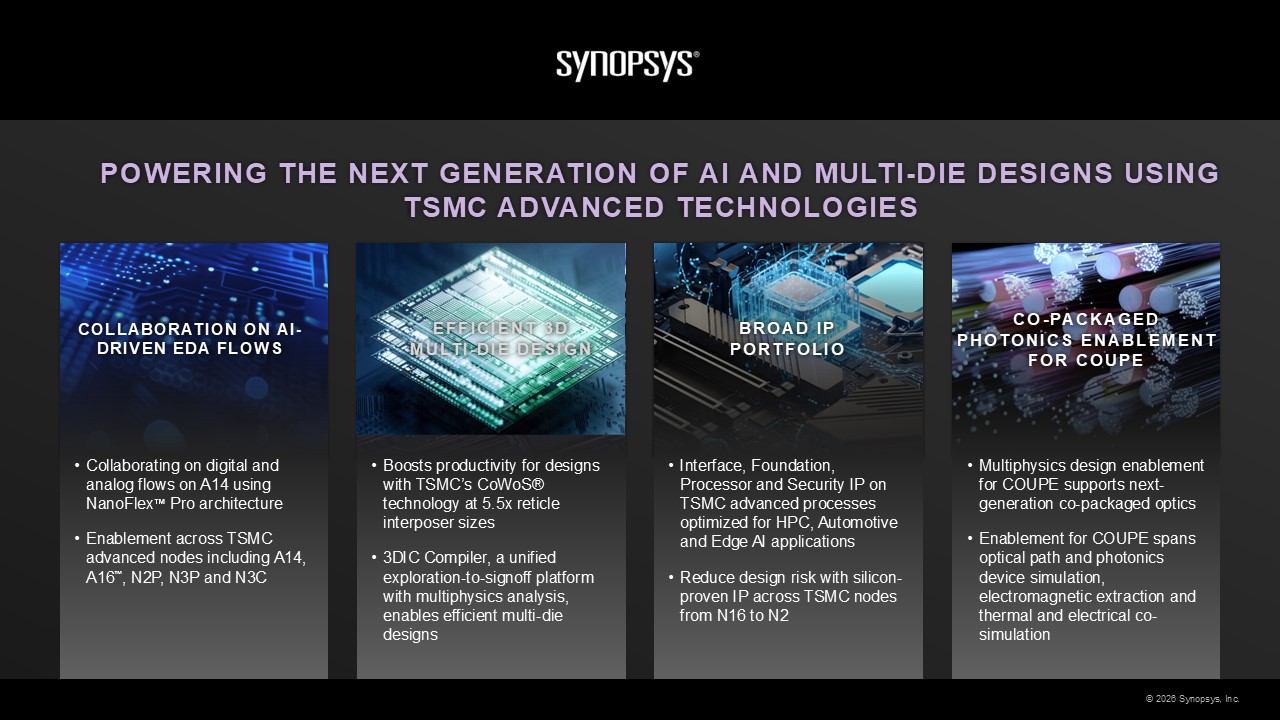

At the core of the announcement is a three-part expansion of capabilities spanning IP, design flows, and system-level enablement.

Synopsys is advancing silicon-proven interface IP validated on TSMC’s most advanced nodes, including 3nm and emerging 2nm-class processes. These include next-generation standards such as M-PHY v6.0 which is now achieving industry-first low-power silicon bring-up on N2P, alongside tapeouts of 64G UCIe IP and 224G high-speed interconnect IP. Together, these technologies form the backbone of AI chips that must move massive volumes of data with minimal latency and power overhead, particularly in bandwidth-constrained environments.

The companies are also extending certified electronic design automation (EDA) flows with a sharper emphasis on increasingly agentic AI-driven optimization. Collaboration on run assistance within Synopsys Fusion Compiler, leveraging TSMC’s A14 process and NanoFlex Pro architecture, is aimed at improving power, performance, and area (PPA) while boosting design productivity. This signals a shift from passive AI assistance toward more active, decision-guiding systems that can materially impact how chips are designed at advanced nodes.

Beyond individual dies, the partnership continues to push into advanced packaging and system-level integration. Synopsys’ 3DIC Compiler platform is now enabling productivity improvements for TSMC’s CoWoS technology at interposer sizes reaching up to 5.5 times the reticle limit, underscoring the scale of modern multi-die designs. This is complemented by multiphysics simulation capabilities that address thermal, electrical, and optical interactions. These requirements are becoming essential as chips evolve into tightly integrated systems.

The announcement also highlights expansion into new application domains. In automotive, Synopsys is offering a UCIe IP solution compliant with ASIL B functional safety requirements on TSMC’s N5A process, marking a significant step toward enabling chiplet-based architectures in safety-critical environments. Meanwhile, advancements in M-PHY IP are targeted at next-generation mobile and storage applications, including smartphones that demand both high performance and power efficiency.

Finally, the collaboration advances AI infrastructure through co-packaged optics. Multiphysics design enablement for co-packaged optical systems, including TSMC’s COUPE design flow, spans optical path simulation, electromagnetic extraction, and system-level analysis, and is paired with 224G IP designed to support optical Ethernet and emerging interconnect standards such as UALink. Together, these capabilities directly address the growing bandwidth and energy challenges facing large-scale AI systems.

Why This Matters for AI Hardware

The significance of this partnership lies in how it tackles the core constraints of modern AI workloads. As compute performance scales, the bottlenecks have shifted toward data movement, power efficiency, and system integration. By combining high-speed IP, agentic AI-driven design tools, and advanced packaging technologies, Synopsys and TSMC are reducing the gap between design complexity and manufacturable silicon.

The introduction of agentic run assistance in EDA tools marks a particularly important inflection point. Rather than simply accelerating existing workflows, these capabilities begin to reshape them, enabling engineers to delegate increasingly complex optimization tasks to AI systems. This has the potential to significantly compress development cycles while improving overall design quality.

Equally critical is the focus on bandwidth. Technologies such as 224G interconnects and co-packaged optics are emerging as key enablers for scaling AI infrastructure, where moving data efficiently is often more challenging than processing it. By integrating these capabilities into both IP and design flows, the partnership addresses one of the most pressing limitations in next-generation AI systems.

The expansion into automotive and mobile markets further underscores the breadth of this strategy. It signals that advanced-node, multi-die, and chiplet-based designs are no longer confined to hyperscale data centers but are beginning to permeate safety-critical and consumer applications as well.

Market And Industry Implications

The expanded alliance reinforces Synopsys’s position as a central player in AI silicon enablement while strengthening TSMC’s ecosystem around its most advanced process nodes. For chip designers, tighter integration between EDA tools and foundry technologies can translate into faster time-to-market and reduced development risk, particularly when targeting cutting-edge nodes.

At the same time, the partnership reflects a broader industry dynamic in which design tools and manufacturing processes are becoming increasingly interdependent. As flows become more deeply optimized and certified for specific nodes, the cost and complexity of switching ecosystems rise. This creates a form of strategic lock-in that benefits tightly aligned partners while raising barriers for competitors.

The Bigger Picture

Taken together, the announcement illustrates a shift in how semiconductor innovation is defined in the AI era. Progress is no longer driven solely by transistor scaling but by the ability to coordinate across multiple layers of the technology stack, from design software and reusable IP to packaging and system integration.

The Synopsys–TSMC collaboration points to a future where chips are conceived not as isolated components but as parts of larger, highly integrated systems spanning data centers, vehicles, and mobile devices. In this landscape, competitive advantage will increasingly depend on how effectively companies can bring together tools, technologies, and partners to deliver complete, optimized solutions.

As AI continues to push the limits of performance and complexity, partnerships like this are likely to define the pace of innovation. The companies that succeed will be those that can bridge the gap between design intent and real-world deployment, turning increasingly sophisticated ideas into scalable, manufacturable systems.

You can access the entire press announcement here.

Also Read:

How to Overcome the Advanced Node Physical Verification Bottleneck

Podcast EP342: The Evolution and Impact of Physical AI with Hezi Saar

WEBINAR: Beyond Moore’s Law and The Future of Semiconductor Manufacturing Intelligence

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.