In the race to deliver ever-larger SoCs under shrinking schedules, simulation is becoming a bottleneck. With debug cycles constrained by long iteration times—even for minor code changes—teams are finding traditional flows too rigid and slow. The problem is further magnified in continuous integration and continuous deployment… Read More

Author: Kalar Rajendiran

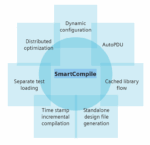

Revolutionizing Simulation Turnaround: How Siemens’ SmartCompile Transforms SoC Verification

Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and Analysis

In a major announcement at the 2025 Design Automation Conference (DAC), Siemens EDA introduced a significant expansion to its electronic design automation (EDA) portfolio, aimed at transforming how engineers design, validate, and manage the complexity of next-generation three-dimensional integrated circuits (3D ICs).… Read More

Siemens EDA Outlines Strategic Direction for an AI-Powered, Software-Defined, Silicon-Enabled Future

In a keynote delivered at this year’s Siemens EDA User2User event, CEO Mike Ellow presented a focused vision for the evolving role of electronic design automation (EDA) within the broader context of global technology shifts. The session covered Siemens EDA’s current trajectory, market strategy, and the changing landscape … Read More

Design-Technology Co-Optimization (DTCO) Accelerates Market Readiness of Angstrom-Scale Process Technologies

Design-Technology Co-Optimization (DTCO) has been a foundational concept in semiconductor engineering for years. So, when Synopsys referenced DTCO in their April 2025 press release about enabling Angstrom-scale chip designs on Intel’s 18A and 18A-P process technologies, it may have sounded familiar—almost expected. … Read More

Andes Technology: Powering the Full Spectrum – from Embedded Control to AI and Beyond

As the computing industry seeks more flexible, scalable, and open hardware architectures, RISC-V has emerged as a compelling alternative to proprietary instruction set architectures. At the forefront of this revolution stands Andes Technology, offering a comprehensive lineup of RISC-V processor solutions that go far beyond… Read More

From All-in-One IP to Cervell™: How Semidynamics Reimagined AI Compute with RISC-V

In an era where artificial intelligence workloads are growing in scale, complexity, and diversity, chipmakers are facing increasing pressure to deliver solutions that are not only fast, but also flexible and programmable. Semidynamics recently announced Cervell™, a fully programmable Neural Processing Unit (NPU) designed… Read More

Andes Technology: A RISC-V Powerhouse Driving Innovation in CPU IP

As it celebrates its 20th anniversary in 2025, Andes Technology stands as a defining force in the RISC-V movement—an open computing revolution. What began in 2005 as a bold vision to deliver high-efficiency Reduced Instruction Set Computing (RISC) processor IP has evolved into a company whose innovations power billions of devices… Read More

Alchip’s Technology and Global Talent Strategy Deliver Record Growth

Alchip Technologies Ltd., a global leader in high-performance computing (HPC) and artificial intelligence (AI) ASIC design and production services, continues its trajectory of rapid growth and technical leadership by pushing the boundaries of advanced-node silicon, expanding its global design capabilities, and building… Read More

Leveraging Common Weakness Enumeration (CWEs) for Enhanced RISC-V CPU Security

As RISC-V adoption accelerates across the semiconductor industry, so do the concerns about hardware security vulnerabilities that arise from its open and highly customizable nature. From hardware to firmware and operating systems, every layer of a system-on-chip (SoC) design must be scrutinized for security risks. Unlike… Read More

Intel’s Foundry Transformation: Technology, Culture, and Collaboration

Intel’s historical dominance in semiconductor process technology began to erode around 2018, as competitors started delivering higher performance at smaller nodes. In response, Intel is now doubling down on innovation across two fronts: advanced process nodes such as Intel 18A and 14A, and cutting-edge packaging technologies.… Read More

Facing the Quantum Nature of EUV Lithography