Noah Sturcken is a Founder and CEO of Ferric with over 40 patents issued and 15 publications on Integrated Voltage Regulators. Noah leads Ferric with focus on business development, marketing and new technology development. Noah previously worked at AMD R&D Lab where he developed Integrated Voltage Regulator (IVR) technology.… Read More

Tag: tsmc

The Sondrel transformation to Aion SIlicon!

Ollie is a commercially astute senior leader with over 20 years of experience in strategy, business development and sales across the technology and engineering sectors, with a strong track record in scaling businesses and driving growth. He has held commercial leadership roles in FTSE 100, private equity-backed, and startup… Read More

SMC 2025 – The Strategic Materials Conference

The New Era of Materials Innovation

The Strategic Materials Conference—SMC offers valuable content and unprecedented networking opportunities for semiconductor industry professionals who share common strategic objectives on materials innovation, management, and business success.

KEYNOTES—EMD Electronics, Microsoft,… Read More

TSMC 2025 China Technology Symposium 2025

Get the latest on:

- TSMC’s industry-leading HPC, Smartphone, IoT, and Automotive platform solutions to advance the AI future

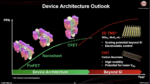

- TSMC’s advanced logic technology progress on 5nm, 4nm, 3nm, 2nm, A16 processes and beyond

- TSMC 3DFabric® advanced silicon stacking and packaging technology advancement on TSMC-SoIC®, InFO,

TSMC Technology Symposium Japan 2025

Japan Technology Symposium

Date

Wednesday, June 11

Time

10:00 a.m. – 6:00 p.m.

Venue

Pacifico Yokohama North, 1-1-2, Minatomirai, Nishi-ku, Yokohama 220-0012, JAPAN

Registration will be closed on 6/4.

VoD (Video on Demand) will be available starting from 7/3.

Registration will close on 7/25.

Get the latest on:

- TSMC’s

Analog Bits at the 2025 Design Automation Conference #62DAC

Analog Bits attends a lot of events. I know because I see them a lot in my travels. Lately, the company has been stealing the show with cutting-edge analog IP on a broad range of popular nodes and a strategy that will change the way design is done. Analog Bits is quietly rolling out a new approach to system design. One that delivers a holistic… Read More

Alchip’s Technology and Global Talent Strategy Deliver Record Growth

Alchip Technologies Ltd., a global leader in high-performance computing (HPC) and artificial intelligence (AI) ASIC design and production services, continues its trajectory of rapid growth and technical leadership by pushing the boundaries of advanced-node silicon, expanding its global design capabilities, and building… Read More

TSMC Europe Technology Symposium 2025

Join us to get the latest on:

- TSMC’s industry-leading HPC, Smartphone, IoT, and Automotive platform solutions to advance the AI future

- TSMC’s advanced logic technology progress on 5nm, 4nm, 3nm, 2nm, A16 processes and beyond

- TSMC 3DFabric® advanced silicon stacking and packaging technology advancement on TSMC-SoIC

TSMC Taiwan Technology Symposium 2025

Get the latest on:

- TSMC’s industry-leading HPC, Smartphone, IoT, and Automotive platform solutions to advance the AI future

- TSMC’s advanced logic technology progress on 5nm, 4nm, 3nm, 2nm, A16 processes and beyond

- TSMC 3DFabric® advanced silicon stacking and packaging technology advancement on TSMC-SoIC®, InFO,

TSMC Describes Technology Innovation Beyond A14

The inaugural event for the 2025 TSMC Technology Symposium recently concluded in Santa Clara, California. This will be followed by events around the world over the next two months. We have summarized information from this event regarding process technology innovation and advanced packaging innovation. Overall, the A14 process… Read More