Part 2 examines the transformation of the interface protocols industry from a fragmented market of numerous specialized vendors to a more consolidated one dominated by a few major solutions providers as driven by the increasing complexity of modern protocols. It highlights the importance of rigorous validation of interface… Read More

Tag: pci express

WEBINAR: Why Rigorous Testing is So Important for PCI Express 6.0

In the age of rapid technological innovation, hyperscale datacenters are evolving at a breakneck pace. With the continued advancements in CPUs, GPUs, accelerators, and switches, faster data transfers are now paramount. At the forefront of this advancement is PCI Express (PCIe®), which has become the de-facto standard of interconnect… Read More

Chiplet Interconnect Challenges and Standards

For decades now I’ve watched the incredible growth of SoCs in terms of die size, transistor count, frequency and complexity. Instead of placing all of the system complexity into a single, monolithic chip, there are now compelling reasons to use a multi-chip approach, like when the maximum die size limit is reached, or it’s… Read More

Data Processing Unit (DPU) uses Verification IP (VIP) for PCI Express

Domain specific processors are a mega-trend in the semiconductor industry, so we see new three letter acronyms like DPU, for Data Processing Unit. System level performance can actually be improved by moving some of the tasks away from the CPU. Companies like Xilinx (Alveo), Amazon (Nitro) and NVIDIA (BlueField) have been talking… Read More

How PCI Express 6.0 Can Enhance Bandwidth-Hungry High-Performance Computing SoCs

What do genome sequencing, engineering modeling and simulation, and big data analytics have in common? They’re all bandwidth-hungry applications with complex data workloads. High-performance computing (HPC) systems deliver the parallel processing capabilities to generate detailed and valuable insights from these applications.

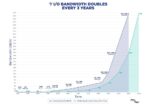

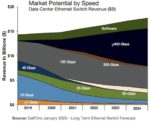

How SerDes Became Key IP for Semiconductor Systems

We have seen that the interface IP category is seeing incredibly high growth rate over the last two decades and we expect this category to generate an ongoing high source of IP revenues for at least another decade. But if we dig into the various successful protocols like PCI Express, Ethernet or USB, we can detect a common function … Read More

Do You Care About What You’re Measuring? Part 2: Cloud Data Centers

When I think about servers and data centers, I think about multiple-core/high-power CPUs, Intel’s domination over the years and GPUs coming on strong in recent years. I think about very fast digital interfaces, such as PCI Express connections and the latest DDR memory interface. Precision analog isn’t something that first comes… Read More

TrueChip CXL Verification IP

TrueChip is a Verification IP specialist. For more than 10 years they have provided verification IP’s, like USB, PCIe, Ethernet, Memory, AMBA, Display RISC V and many more. They have an extensive portfolio including a very interesting product that is “TruEYE™️ GUI” which is a debugger helper tool for the verifications IPs.

Protocol

… Read MorePCI Express in Depth – Transaction Layer

In the last article i write about the Data Link Layer, in this article i’ll write about the Transaction Layer.

This layer’s primary responsibility is to create PCI Express request and completion transactions. It has both transmit functions for outgoing transactions, and receive functions for incoming transactions.… Read More

PCI Express in Depth – Data Link Layer

In the last article, i wrote about the physical layer, now let’s take a look in the next layer the data link layer.

The Data Link Layer serves as the “gatekeeper” for each individual link within a PCI Express system. It ensures that the data being sent back and forth across the link is correct and received in the same order it