Synopsys has expanded its ARC processor portfolio to include a family of RISC-V processors. This was originally reported on SemiWiki last October. There is also a recent in-depth article on the make-up of the ARC-V family on SemiWiki here. This is important and impactful news; I encourage you to read these articles if you haven’t done so already. What I want to cover in this post is a broader perspective on what Synopsys is doing to provide holistic support for the entire processor ecosystem. I’ve always felt that the market leader should be expanding the market, creating new opportunities for not just itself, but for its current and future customers as well as the entire ecosystem at large. This is such a story. Follow the leader to see how Synopsys provides broad support for processor ecosystems.

The Organizational View

The org chart for a company can tell a lot about strategy. In the case of support for the processor ecosystem at Synopsys there is information to be gleaned here. About two years ago, Kiran Vittal was named the Executive Director, Ecosystem Partner Alliances Marketing at Synopsys. In this role, Kiran has the charter to work with IP partners, foundry partners, EDA partners and the rest of Synopsys to optimize the EDA tool flows and associated IP for the markets served. Note there is no specific charter regarding, Arm, ARC or RISC-V. Kiran has it all. This organizational setup is an important ingredient to facilitate holistic support for an entire ecosystem. Just the way a market leader should.

I’ve known Kiran for quite a while. We worked together at Atrenta (the SpyGlass company) before it was acquired by Synopsys. Kiran has exactly the right personality and technical depth (my opinion) to do this rather challenging job. Recently, I was able to speak with Kiran to get a long-overdue update. Here are some of the things I learned.

What Holistic Support Looks Like

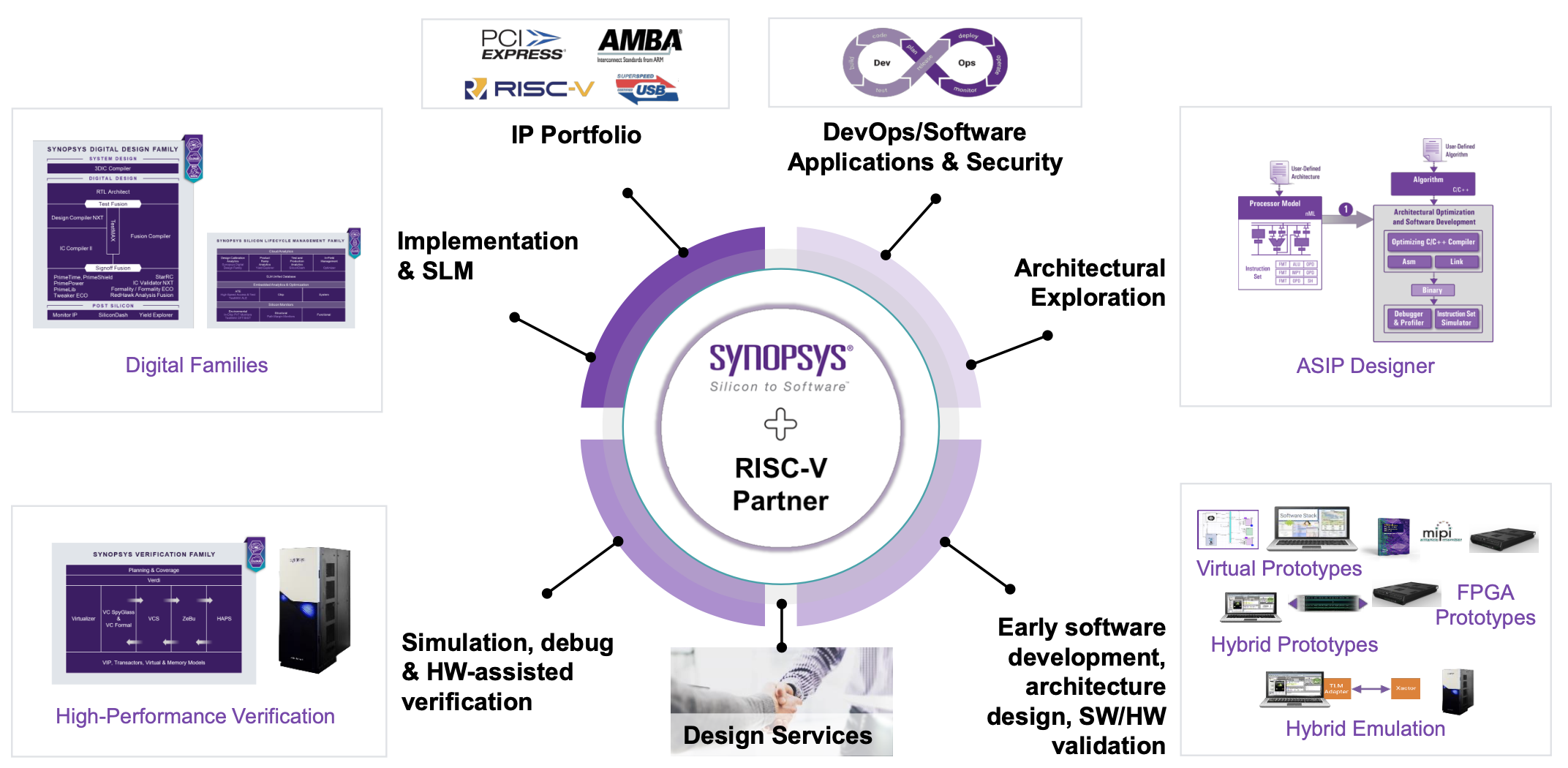

Kiran began by describing the broad support Synopsys offers for implementation and verification for the growing RISC-V market. The strategy covers a lot of ground across architectural exploration, IP support, software development, DevOps, HW/SW verification, design servicers and a broad suite of simulation and verification methodologies. The figure below summarizes all this.

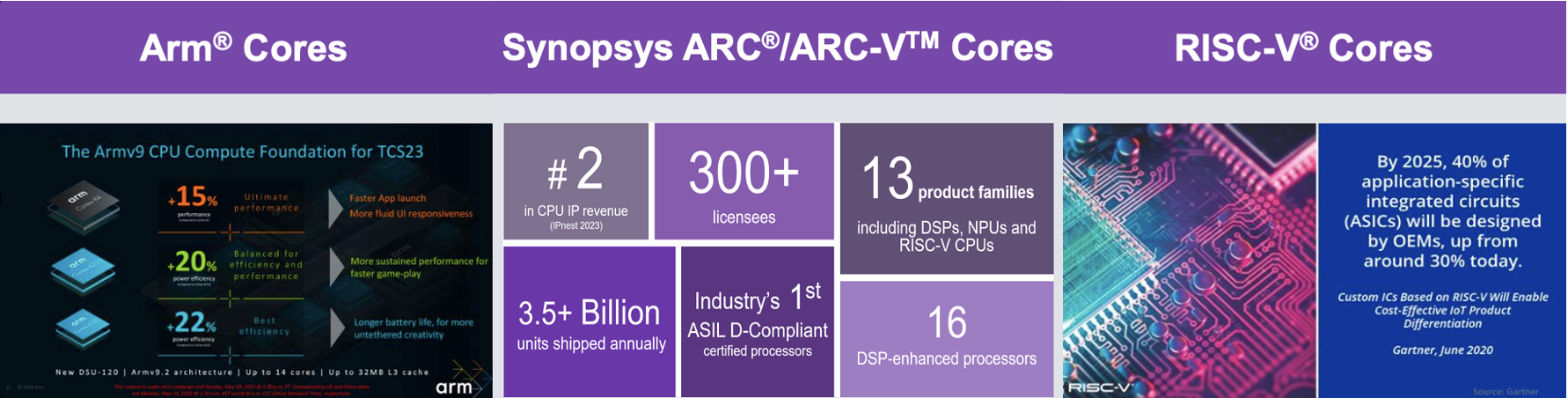

As I mentioned earlier. Kiran’s perspective is NOT limited to the RISC-V market. Arm has also been a strong partner for many years. There is plenty going on across the spectrum of processor options. The graphic at the top of this post is a high-level summary of this strategy. Some details are useful:

For Arm

- Deep collaboration on advanced nodes down to 2nm

- Fusion QuickStart Kits & verification collateral available for latest cores

- Opportunity to tune the cores to get the best out-of-the-box PPA

For Synopsys ARC/ARC-V

- Enablement of ARC/ARC-V cores with Synopsys digital design and verification families

- Fusion QuickStart Kits for high-performance ARC/ARC-V cores

- Design services for customer enablement

For RISC-V Cores

- Partnering with key customers, RISC-V core providers, foundries and universities

- Building customized flows for implementation and verification

- Fusion QuickStart Kits (QIKs) with SiFive® available now

Kiran explained that Synopsys has a growing list of ARC-V customers, but there are also a lot of customers who have chosen to source processor IP from other vendors. Once the customer chooses the processor IP, Synopsys can provide a rich set of EDA tools, flows and IP to support that choice. It is true that ARC has been part of Synopsys for quite a while. That means all ARC products enjoy a tight integration and validation with Synopsys tools and IP.

While this does provide a competitive advantage, Synopsys still maintains strong relationships across the processor ecosystem to ensure a rich experience regardless of processor choice. As we had this discussion, I kept thinking about my view of the way a market leader behaves.

There is a lot more to the ARC-V story. I’ll be providing links to learn more in a moment. But first, I want to share a really interesting case study regarding a RISC-V design.

AI Impact on Processor Design

AI is finding its way into every part of our lives. If you design advanced processors, this is true as well. Here are some compelling details for an AI-driven optimization of a RISC-V high performance CPU core.

The design is a RISC-V based “Big Core” targeted for data center applications. Its size is 426umx255um for a single core. The target process technology is 5nm. The baseline (starting point) for this exercise was 1.75GHz at 29.8mW of power. This represents the out-of-the-box results from a RISC-V reference flow.

The desired target for this design was 1.95GHz at 30mW of power. The customer estimated hitting this target would take about one month for two expert engineers. Applying the Synopsys DSO.ai AI-driven RISC-V reference flow, 1.95GHz at 27.9mW of power was achieved over two days and 90 software runs, with no human effort. The expected area target was also met.

This is what the future of processor design looks like.

To Learn More

If you want to learn more about the Synopsys ARC-V processor IP family, you can find it here. If you want to step back and look at the overall processor solutions available from Synopsys, look here or you can learn about the Synopsys overall strategy to support RISC-V here. And if you want to learn more about the revolutionary DSO.ai capability from Synopsys, check out this link. And that’s how you can follow the leader to see how Synopsys provides broad support for processor ecosystems.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.