Reports out of Taiwan (I’m in Hsinchu this week) have TSMC more than doubling 28nm wafer output in Q3 2012 due to yield improvements and capacity increases while only spending $3.6B of the $8.5B forecasted CAPEX! Current estimates have TSMC 28nm capacity at 100,000 300mm wafers (+/- 10%) per month versus 25,000 wafers reported… Read More

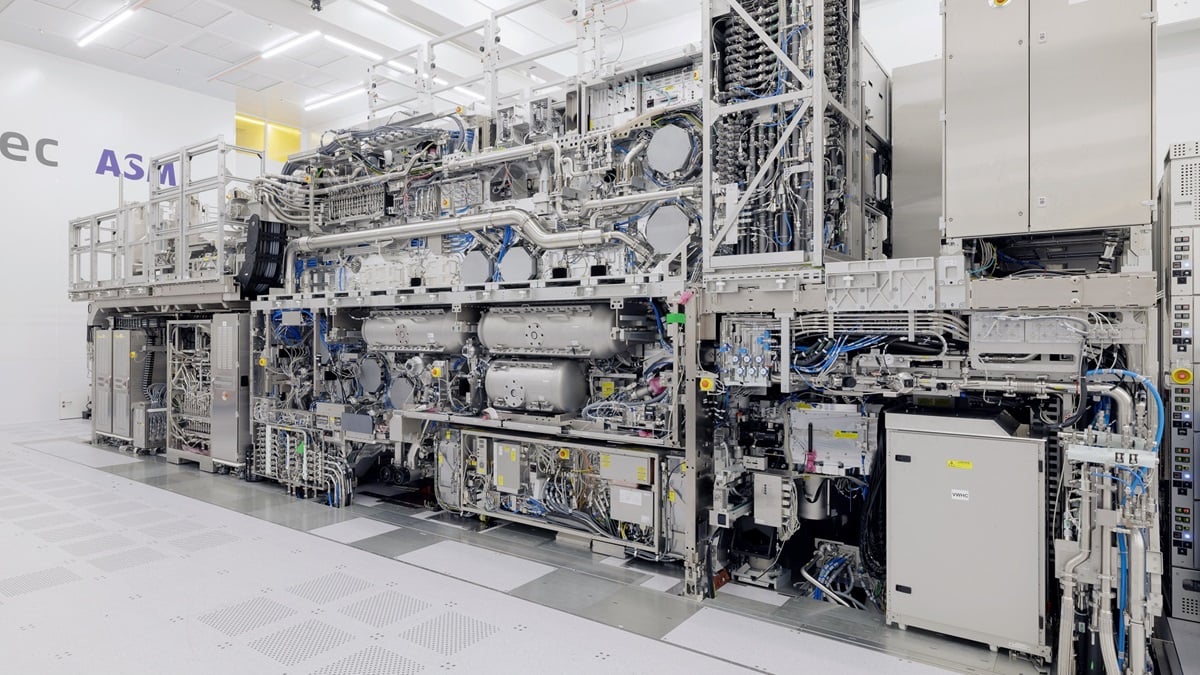

ASML- Soft revenues & Orders - But...China 49% - Memory ImprovingASML- better EPS but weaker revenues- 2024 recovery…Read More

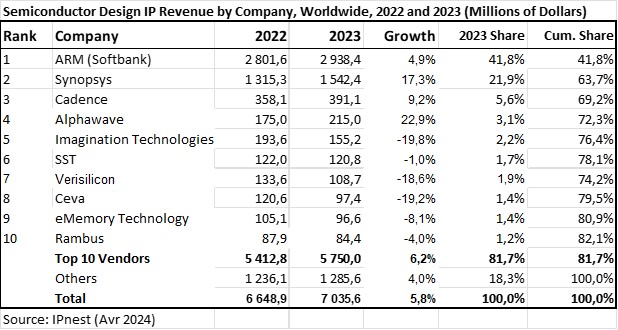

ASML- Soft revenues & Orders - But...China 49% - Memory ImprovingASML- better EPS but weaker revenues- 2024 recovery…Read More Semi Market Decreased by 8% in 2023… When Design IP Sales Grew by 6%!Design IP revenues had achieved $7.04B in 2023,…Read More

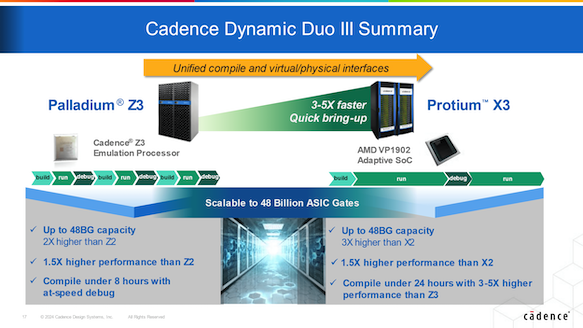

Semi Market Decreased by 8% in 2023… When Design IP Sales Grew by 6%!Design IP revenues had achieved $7.04B in 2023,…Read More Cadence Debuts Dynamic Duo III with a Basket of GoodiesI am a fan of product releases which…Read More

Cadence Debuts Dynamic Duo III with a Basket of GoodiesI am a fan of product releases which…Read More CEO Interview: Khaled Maalej, VSORA Founder and CEOKhaled Maalej is founder and CEO of VSORA,…Read More

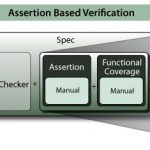

CEO Interview: Khaled Maalej, VSORA Founder and CEOKhaled Maalej is founder and CEO of VSORA,…Read MoreAssertion Synthesis

In June, Atrenta acquired NextOp, the leader in assertion synthesis. So what is it?

Depending on who you ask, verification is a huge fraction, 60-80%, of the cost of an SoC design, so obviously any technology that can reduce the cost of verification has a major impact on the overall cost and schedule of a design. At a high-level, verification… Read More

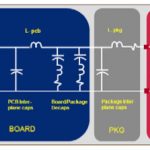

Power, Signal, Thermal and EMI signoff

Increasingly the challenge with SoCs, especially for mobile, is not getting the performance high enough but doing so in a power-efficient manner. Handheld devices running multiple apps need high-speed processors that consume extremely low levels of power both in operating and standby modes. In the server farm, the limit is … Read More

Apple’s Victory Will Re-Shuffle the Semi Industry

Apple’s legal victory over Samsung has been analyzed in thousands of articles and TWEETs since last Friday’s announcement and surely more will follow. Most of the commentary has focused on the first order impact to handset manufacturers. It is not entirely clear how it will all settle but there are sure to be secondary ramifications… Read More

A Brief History of FPGAs

From the transistor to the integrated circuit to the ASIC, next comes programmable logic devices on the road to the mainstream fabless semiconductor industry. PLDS started in the early 1970’s from the likes of Motorola, Texas Instruments, and IBM but it wasn’t until Xilinx brought us the field programmable gate array (FPGA)… Read More

SpringSoft Laker vs Tanner EDA L-Edit

Daniel Payne recently blogged some of the integration challenges facing Synopsys with their impending acquisition of SpringSoft. On my way back from San Diego last week I stopped by Tanner EDA to discuss an alternative tool flow for users who find themselves concerned about the Laker Custom Layout road map.

Design of the analog… Read More

IP Wanna Go Fast, Core Wanna Not Rollover

At a dinner table a couple years ago, someone quietly shared their biggest worry in EDA. Not 2GHz, or quad core. Not 20nm, or 450mm. Not power, or timing closure. Call it The Rollover. It’s turned out to be the right worry.

Best brains spent inordinate hours designing and verifying a big, hairy, heavy breathing processor core to do … Read More

A Brief History of ASIC, part II

All semiconductor companies were caught up in ASIC in some way or another because of the basic economics. Semiconductor technology allowed medium sized designs to be done, and medium sized designs were pretty much all different. The technology didn’t yet allow whole systems to be put on a single chip. So semiconductor companies… Read More

Book Review: Mixed-Signal Methodology Guide

Almost every SoC has multiple analog blocks so AMS methodology is an important topic to our growing electronics industry. Authored by Jess Chen (Qualcomm), Michael Henrie (Cliosoft), Monte Mar (Boeing) and Mladen Nizic (Cadence), the book is subtitled: Advanced Methodology for AMS IP and SoC Design, Verification and Implementation… Read More

Book Review: Mixed-Signal Methodology guide

Almost every SoC has multiple analog blocks so AMS methodology is an important topic to our growing electronics industry. Authored by Jess Chen (Qualcomm), Michael Henrie (Cliosoft), Monte Mar (Boeing) and Mladen Nizic (Cadence), the book is subtitled: Advanced Methodology for AMS IP and SoC Design, Verification and Implementation… Read More

Real men have fabs!