EDA software for IC and system design became a commercial business in the early 1980s. In those days, 3 companies – Daisy Systems, Mentor Graphics, and Valid Logic Systems – dominated the emerging EDA industry. However, two small startups that emerged in the early 1980s grew rapidly and merged to form Cadence Design Systems in 1988.… Read More

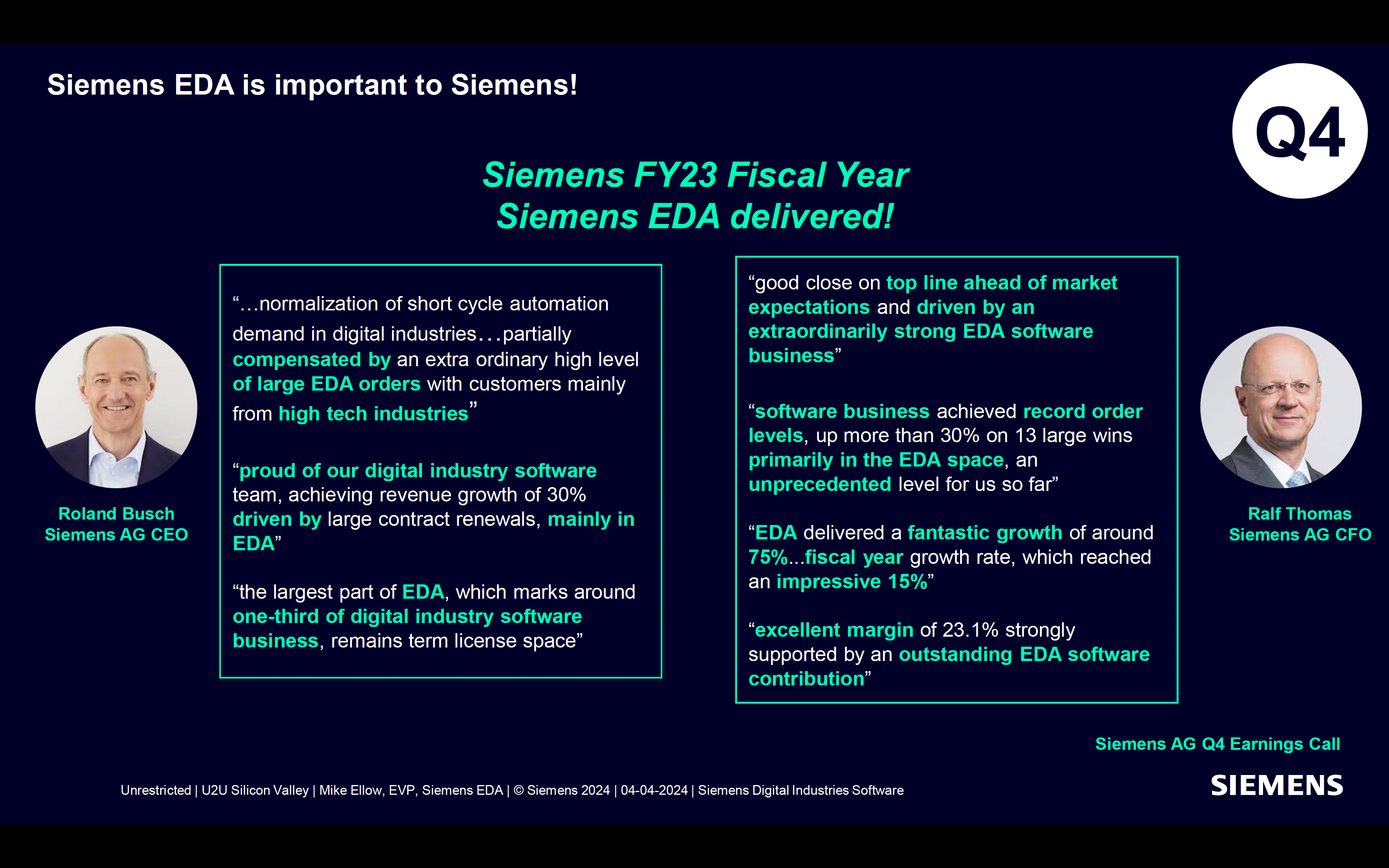

Enabling Imagination: Siemens' Integrated Approach to System DesignIn today's rapidly advancing technological landscape, semiconductors are…Read More

Enabling Imagination: Siemens' Integrated Approach to System DesignIn today's rapidly advancing technological landscape, semiconductors are…Read More Ceva Accelerates IoT and Smart Edge AI with a New Wireless Platform IP FamilyCeva is a very focused company. In its…Read More

Ceva Accelerates IoT and Smart Edge AI with a New Wireless Platform IP FamilyCeva is a very focused company. In its…Read More LRCX- Mediocre, flattish, long, U shaped bottom- No recovery in sight yet-2025?- Lam reports another flat quarter & guide-…Read More

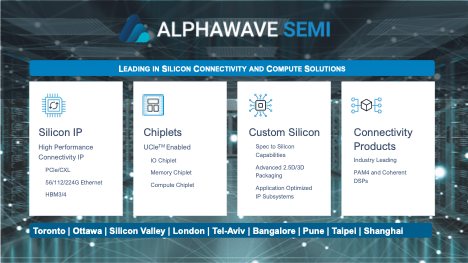

LRCX- Mediocre, flattish, long, U shaped bottom- No recovery in sight yet-2025?- Lam reports another flat quarter & guide-…Read More Alphawave Semi Bridges from Theory to Reality in Chiplet-Based AIGenAI, the most talked-about manifestation of AI these…Read More

Alphawave Semi Bridges from Theory to Reality in Chiplet-Based AIGenAI, the most talked-about manifestation of AI these…Read MoreThe Need for OASIS in Post-layout IC Databases

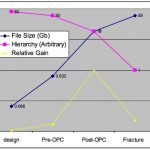

OASIS is a hierarchical IC file format used for IC designs that is gradually replacing GDS II throughout the mask data stages. The compelling reason for using OASIS has always been the reduction of file size, and speed up of processing times through the use of hierarchy and fewer translation steps.

At the 45nm node an actual M1 layer… Read More

Toshiba Corp. has cancelled plans to sell (ARM-based processor) computers …bad news for Toshiba, TI and the end user

This news announced two weeks ago is not really good news for those expecting to see this new generation of computers, running Windows RT OS and no more based on x86 processor but on ARM CPU core, coming on the market. The reason invoked by Toshiba was “delays in getting adequate supplies of components” and, even if Toshiba did not specifically… Read More

Arteris joins Inc. 500 List of America’s Fastest-Growing Private Companies… thanks to Arteris customers!

Arteris, founded in 2003, is the inventor and leading supplier of network-on-chip (NoC) interconnect IP solutions. Can we say that the company is still a start-up? I would say yes, as their flagship product, FlexNoc (Network on Chip IP function) was a completely new concept when it was introduced. As for every disruptive technology,… Read More

Did Qualcomm and Apple Attempt to Bribe TSMC?

It’s amazing how these rumors start and go viral. People are literally laughing here in Taiwan. I remember I wrote something that I thought was obviously satire and less than a week later someone repeated it back to me as fact since they “read it on the internet somewhere.”

According to Bloomberg: Apple Inc. (AAPL) and Qualcomm Inc.… Read More

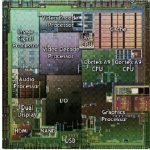

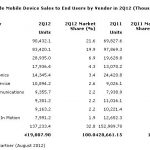

Smart mobile SoCs: Made in China

One of the comments to previous installments of this series was that there isn’t much left for the merchant suppliers of smart mobile SoCs, considering Apple and Samsung have majority share and design their own parts. The theory is this makes it hard for many suppliers to continue investing at the resource levels needed to bring … Read More

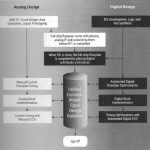

Mixed-Signal Methodology Guide

Last week I reviewed Chapter 1 in the new book: Mixed-Signal Methodology Guide, and today I finish up my review of Chapters 2 through 11. You can read the entire book chapter by chapter, or just jump directly to the chapters most related to your design role or project needs. With multiple authors I was impressed with the wide range of… Read More

Mixed-Signal Methodology Guide

Last week I reviewed Chapter 1 in the new book: Mixed-Signal Methodology Guide, and today I finish up my review of Chapters 2 through 11. You can read the entire book chapter by chapter, or just jump directly to the chapters most related to your design role or project needs. With multiple authors I was impressed with the wide range of… Read More

TSMC 28nm Update Q3 2012!

Reports out of Taiwan (I’m in Hsinchu this week) have TSMC more than doubling 28nm wafer output in Q3 2012 due to yield improvements and capacity increases while only spending $3.6B of the $8.5B forecasted CAPEX! Current estimates have TSMC 28nm capacity at 100,000 300mm wafers (+/- 10%) per month versus 25,000 wafers reported… Read More

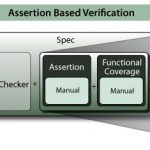

Assertion Synthesis

In June, Atrenta acquired NextOp, the leader in assertion synthesis. So what is it?

Depending on who you ask, verification is a huge fraction, 60-80%, of the cost of an SoC design, so obviously any technology that can reduce the cost of verification has a major impact on the overall cost and schedule of a design. At a high-level, verification… Read More

Why NA is Not Relevant to Resolution in EUV Lithography