The IC industry is commonly divided into different market segments – consumer, mobile, industrial, commercial, medical, automotive, and aerospace. A key differentiation among these segments is the characterization and reliability qualification strategy for the fabrication process and design circuitry. For each segment, specific voltage and temperature environment ranges are input to electrical characterization and analysis flows to confirm functional operation. Reliability analysis expands upon these circuit characterization parameters to evaluate various failure mechanisms, which can lead to either “hard error” lifetime fails or “soft error” transient fails. The primary lifetime failure mechanisms are related to device and interconnect parameter drift due to “aging”, associated with: the number of power-on hours; the on/off (thermal) cycles; interconnect current density; and, circuit switching activity. The primary source of soft errors is due to exposure to external radiation.

I was curious to learn more about the aerospace segment – but first, I needed to study up on radiation-hardened (“rad hard”) soft error concerns and circuit design.

Rad Hard Design

Over the evolution of VLSI process technologies, failure diagnosis and experimental research has identified two principal sources of radiation-induced soft errors:

- alpha particles incident on sensitive circuit nodes

- cosmic ray-generated high-energy neutrons

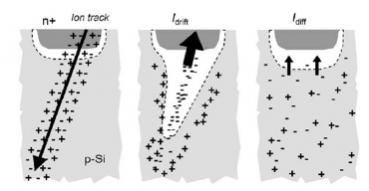

IC industry veterans will remember the crucial time in the 1970’s when DRAM “soft error upsets” (SEU) were a dominant failure mechanism. Groundbreaking research identified the root cause as the introduction of free electron-hole pairs generated by an incident radiated alpha particle, which creates an “ionization track” as it traverses the silicon, as illustrated in the figure below.

Figure 1. An illustration of the “ionization track” due to an incident alpha particle at an nFET device node. The principal charge collection mechanism is the drift due to the depletion region electric field. (From Autran, et al, “Soft-Error Rate of Advanced SRAM Memories: Modeling and Monte Carlo Simulation”.)

If these free carriers are generated in the critical “collection volume” associated with a depletion region electric field, the charges would drift to a circuit node, significantly disrupting the node voltage. (The electric field drift mechanism would be stronger than the diffusion of the free charge distribution.)

Fast forwarding several decades, many technical advances have been made to reduce the SEU rate:

- packaging and die-package attach materials improvements reduce the flux of alpha particles from radioactive decay

- with process/voltage scaling, the collection volume has decreased (although so has the critical charge, Qcrit, on dynamic storage nodes)

- DRAM architectures have added ECC functionality to correct single-bit errors

- systems have implemented memory scrubbing operations

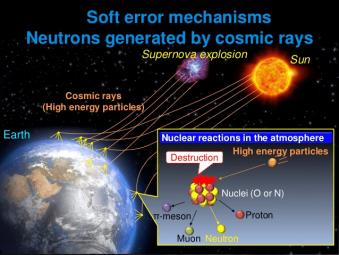

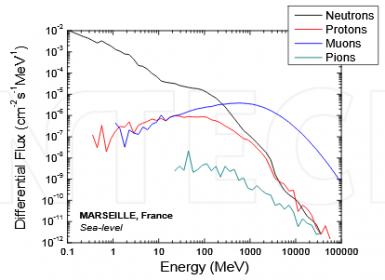

Today, the principal cause of SEU is due to the incident flux of cosmic radiation – the figure below illustrates the constituent high-energy particles.

Figure 2. Cosmic rays generate high-energy neutrons, which have an extremely long range. (From NTT Systems Laboratories, “The action against soft-errors to prevent service outages”.)

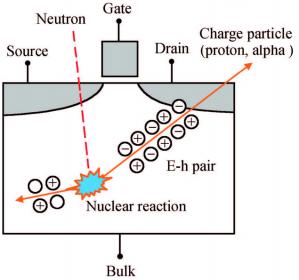

The key contribution to SEU is from the neutron flux incident on a die. A neutron collision with the silicon lattice may result is a permanent displacement which is a hard fail lifetime consideration, especially for bipolar devices (due to increased recombination rates in the base junction). Of principal concern for CMOS devices, a neutron collision may generate (high-energy) secondary particles, which can then create free electron-hole pairs resulting in an SEU, in a manner similar to alpha particles.

Figure 3. Illustration of an inelastic neutron collision with the silicon lattice, and (charged) secondary particles creating free electron-hole pairs. (From Yuanfu, et al., “Single event soft error in advanced integrated circuit”.)

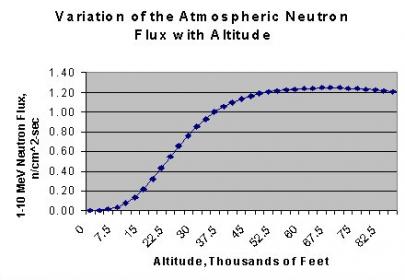

A specific consideration is that the high-energy neutron flux is much greater at high altitude, where aerospace equipment will be operating.

Figure 4. Neutron flux (1-10MeV momentum) versus altitude. (From KVA Engineering)

Figure 5. Neutron momentum versus flux rate, measured at sea level. (From Autran, et al.)

Radiation-hardened circuit development is focused on reducing the susceptibility to the impact of an ionizing event. SRAM bit cell and flip-flop circuits are designed to increase the Qcrit over their equivalent commercial library offerings. The circuit layouts are developed to minimize the collection volume, specifically the sensitive node area, and the magnitude of the depletion region electric field to the node.

The Aerospace Market and eFPGA’s

I knew the aerospace market was a big user of FPGA technology, so I reached out to the team at Flex Logix, developers of embedded FPGA IP, for their insights. I recently had the opportunity to chat with Geoff Tate, CEO, and Andy Jaros, VP of Sales, and learned a great deal.

Geoff had some very interesting financial data, indicating, “10% of the FPGA market revenue is from the aerospace segment. And, FPGA’s represent 35% of the electronics cost in aerospace products. FPGA’s are especially appealing due to the reconfigurability, as these products have a long deployment lifetime. Currently, there are very few commercial FPGA products qualified for the aerospace market.”

Andy added, “Aerospace companies have unique requirements for electronics, with regards to performance, power, and product volume.” (We are all aware that mobile product applications are extremely sensitive to cubic volume – I hadn’t thought much about aerospace-related designs, but they certainly are, as well.)

Andy continued, “For these reasons, there is a need to pursue technology integration, but the individual unit volume is relatively low. That’s why we are seeing strong interest from aerospace developers in leveraging embedded FPGA technology – providing for both integration and reconfigurability.”

“What about the rad hard requirements?” I asked.

Geoff said, “Our eFPGA architecture is extremely modular, allowing us to readily embed rad hard library cells into the LUT design, and rad hard bit cells into the SRAM. We recently completed a collaborative project with an aerospace Licensee, where we took their library and re-implemented the EFLX core into a rad hard implementation, with a preferred metallization stack. All the eFPGA synthesis and compiler support remains the same. We re-extracted and re-characterized the power/performance to the aerospace environment. All within a matter of a few months.”

Given a rad hard circuit library, the recent Flex Logix Technologies collaboration demonstrates that developing an eFPGA for aerospace products is achievable quickly and with low cost.

Considering the traditional appeal of FPGA’s for this segment, and the benefits of technology integration, I anticipate there will be more announcements in the near future. For additional information on aerospace applications for eFPGA’s, please follow this link.

PS. The DAC and ICCAD conferences are the premier places to learn about the latest in EDA tools research. Advanced process technology presentations are the highlight of the IEDM conference. For aerospace product developers, I learned from Geoff and Andy that the GOMACTech conference is the place to be: https://www.gomactech.net/2018/index.html . If you happen to be attending GOMACTech 2018, be sure to stop by the Flex Logix booth and say “Hi!”.

-chipguy

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.