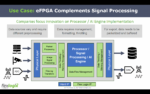

Field-Programmable Gate Arrays (FPGAs) have long been celebrated for their unmatched flexibility and programmability compared to Application-Specific Integrated Circuits (ASICs). And the introduction of Embedded FPGAs (eFPGAs) took these advantages to new heights. eFPGAs offer on-the-fly reconfiguration capabilities,… Read More

Tag: eflx

High Efficiency Edge Vision Processing Based on Dynamically Reconfigurable TPU Technology

While many tough problems relating to computing have been solved over the years, vision processing is still challenging in many ways. Cheng Wang, Co-Founder and CTO of FlexLogix Technologies gave a talk on the topic of edge vision processing at Linley’s Spring 2022 conference. During that talk he references how Gerald Sussman… Read More

Neural Network Efficiency with Embedded FPGA’s

The traditional metrics for evaluating IP are performance, power, and area, commonly abbreviated as PPA. Viewed independently, PPA measures can be difficult to assess. As an example, design constraints that are purely based on performance, without concern for the associated power dissipation and circuit area, are increasingly… Read More

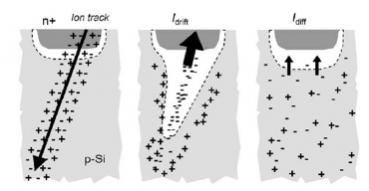

Adapting an embedded FPGA for Aerospace Applications

The IC industry is commonly divided into different market segments – consumer, mobile, industrial, commercial, medical, automotive, and aerospace. A key differentiation among these segments is the characterization and reliability qualification strategy for the fabrication process and design circuitry. For each segment,… Read More

The eFPGA Market is Heating Up!

It is nice to see an emerging market successfully emerge for a change. With embedded FPGAs we are way past test chips and are now seeing tape-outs and silicon in a variety of applications. I’m not sure what the current market estimate of eFPGA is just yet but they align nicely with the $30B+ micro controller market. Market studies have… Read More

One chip and the MCU variant challenge disappears

Merchant microcontrollers are usually made available in a wide range of variants based on one architecture with different peripheral payloads and packaging options. A couple of companies, notably Cypress with their PSoC families and Silicon Labs with the EFM8 Laser Bee… Read More

Adding DSP hardware shrinks energy for MCU core

ARM’s Cortex-M4 processor core represented quite a breakthrough in digital signal controller technology when launched in 2010. Adding a single-cycle multiplier and SIMD instructions enabled basic DSP algorithms while retaining the low power benefits of an MCU. New technology circa 2016 – embedded programmable logic – can… Read More

Flex Logix validating EFLX on TSMC 40ULP

Flex Logix has been heads-down for the last several months working toward customer implementations of their EFLX reconfigurable RTL IP cores. Today, they’ve announced a family of 10 hard IP cores ready in TSMC 40ULP, and provided an update to their roadmap for us.… Read More

Fast Track to a reconfigurable ASIC design

Licensing IP can be a pain, especially when the vendor’s business model has front-loaded costs to get started. Without an easy way to evaluate IP, justifying a purchase may be tough. With more mid-volume starts coming for the IoT, wearables, automotive, and other application segments, it’s a growing concern. Flex… Read More

Creating a better embedded FPGA IP product

Our introduction to Flex Logix and its embedded FPGA core IP drew several comments, predominantly along the lines of a few things like this have been tried before. In this installment, we dive into the EFLX cores, the FPGA toolchain, the roadmap, and a powerful integration feature.… Read More