Earlier in April, Achronix made a product announcement with the headline “Achronix Now Shipping Industry’s Highest Performance Speedster7t FPGA Devices.” The press release drew attention to the fact that the 7nm Speedster®7t AC7t1500 FPGAs have started shipping to customers ahead of schedule. In the complex product world of semiconductors, hitting a production silicon milestone ahead of schedule is a significant accomplishment. The copy stated that the product includes innovative architectural features making it ideal for data acceleration applications. It also spotlighted the industry’s first 2D network-on-chip (NoC), an architectural innovation that eliminates complex routing bottlenecks found in traditional FPGAs. Amid these highlighted aspects, it is easy to miss the bigger story.

No, I’m not talking about the upcoming SPAC merger with ACEV to become a publicly traded company. Yes, that’s a significant story as well and portends to bring lot of benefits to Achronix’s customers. But there is an even bigger story. And that story is about the effect Achronix’s solutions and product strategy are expected to have on the industry. In order to fully appreciate the potential impact, we have to review the changes that have taken place from the 1980s to today. That backdrop will provide the rationalization for what, why and how Achronix’s timeless solutions are expected to solve long standing chronic problems.

1980s to Now

Market Evolution:

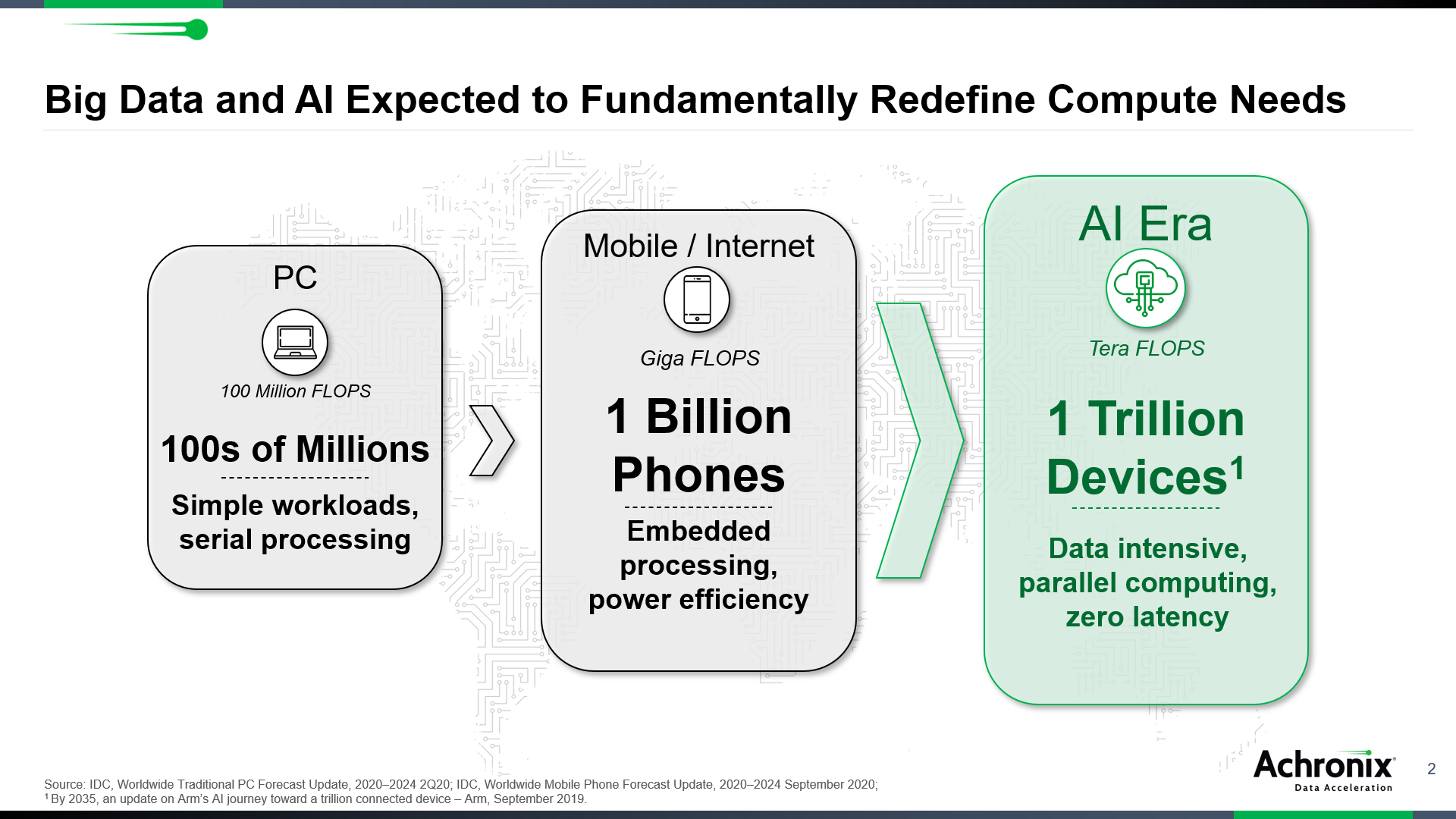

There was a time when integrated circuit (IC) chips used to be referred to as computer chips. That is because there was only one market and that was the computing market. Product performance was critical. Cost and power consumption were secondary. That was the situation, say up through the 1980s. From the 1990s, communications market started growing rapidly. Product performance was still a dominant driver although cost also started becoming important. From the 2000s, consumer market for electronic products started growing rapidly. Cost and power consumption became dominating factors. The late 2000s saw the lines between computing, communications and consumer markets fade away in a major way. From the 2010s, big data, e-commerce, data security and cloud computing became major drivers. And starting around 2015, we entered the artificial intelligence (AI) era and emphasis of edge computing paradigm. Refer to Figure below.

But this evolution did not lead to a super-monolithic market segment. On the contrary, a number of smaller market segments have been created with requirements primarily driven by the use case the devices are deployed for.

Semiconductor process node/technology:

In order to support the above market evolution, foundries have been pushed to develop multiple flavors of a process node, one for high performance/speed, one for low power, one for ultra-low power, etc.,

Chip Design Cost and Cycle Times:

With the introduction of each advanced process node, chip design cycle time got longer. And chip design cost went higher.

Market Attraction for ASICs:

ASIC-based product attractiveness was a no brainer when the target market segment was large, the development cost was low and the design cycle time was short. This was the case up until the early 2010s. As the market evolved, monolithic large market segments fragmented into many smaller ones. This combined with increased development cost and longer design cycle time, made it difficult to make a business case for ASICs.

Product Cycles:

Electronic product cycles that used to be around three years back in the 1990s started getting shorter and shorter. With explosive growth in AI driven applications and rapid advances in AI techniques, product cycles got compressed tremendously.

Market Attractiveness for traditional FPGAs:

Although the founding of the ASIC market and the traditional FPGA market happened in the 1980s, both markets did not experience the same growth path. For a long period, FPGAs were predominantly used for prototyping and in low-volume, high-margin products. It remained this way until the communications market started taking off and high-speed I/O were added to FPGAs.

Chronic Problems:

Processors: Consume too much power as a tradeoff for maximum flexibility

ASICs: Lack of flexibility (once implemented) as a tradeoff for optimized performance and power

Traditional FPGAs: Not as optimized as ASICs, not as flexible as processors, intrachip performance bottlenecks.

ASSPs: Not as optimized as ASICs as a tradeoff for amortizing R&D cost over a larger market

Now and Onward

What if we can solve the chronic problems without too much of a tradeoff? How about increasing addressable market size and extending product life without having to re-spin silicon?

With the market moving toward an AI driven, edge-centric, fast-changing, data-accelerated product space with short life cycles, the stage is set for a timeless solution to fill the demand. The increased interest in leveraging a chiplet methodology for developing semiconductor products is not a coincidence.

Achronic (timeless) Solutions:

Achronix through its ACE design tools and partner tools ecosystem, makes it easy for customers to design their products. Customers may tap from the Speedster® family of products that eliminates traditional FPGA problems. Customers could also tap from Achronix’s various eFPGA cores to implement their products and eliminate other chronic problems. I expect product developers to adopt chiplets methodology and eFPGAs incorporation as and when applicable. In essence, customers could achieve earlier tape-out, address more SKUs and extend product lifecycle.

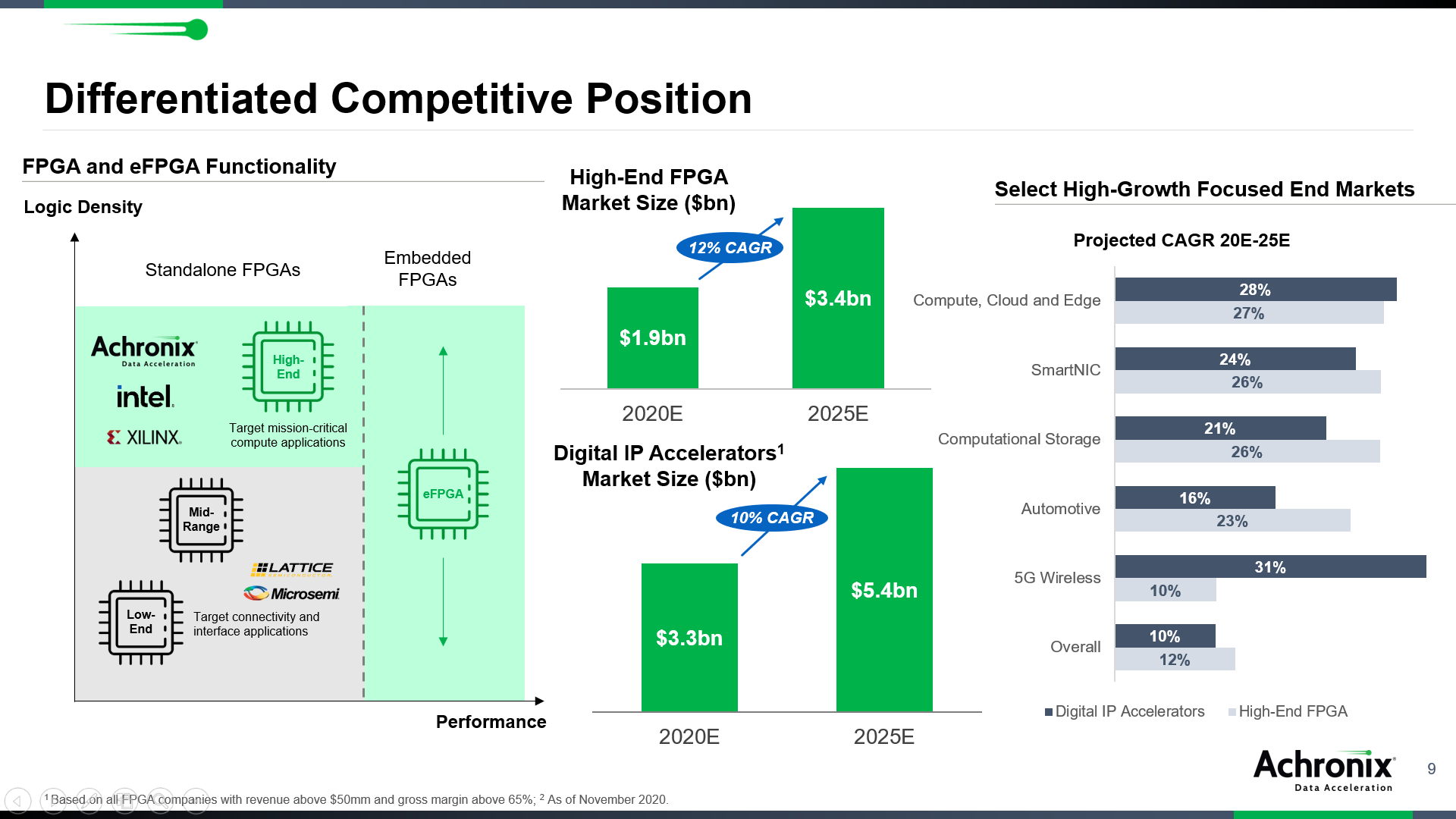

If you are developing products in any of these high-growth, fast changing markets (refer to above figure), you may want to explore ways to benefit from Achronix’s offerings by holding deep dive discussions with them.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.