FPGA prototyping and hardware emulation originated from two independent demands that emerged at roughly the same time, namely, the necessity to implement digital designs in reconfigurable hardware. This was conceivable given the newly introduced field programmable gate array (FPGA) device.

Yet from the very beginning they… Read More

Verification Futures UK 2026, co-located with Semiconductors Futures 2026 organised by Tessolve and co-organised this year with Alpinum. The conference continues its strong tradition of delivering a unique blend of conference presentations, exhibitions, training, and industry networking sessions focused on the challenges… Read More

In an era where product differentiation increasingly depends on performance, power efficiency, and form factor, Application-Specific Integrated Circuits (ASICs) have become the ultimate competitive weapon for innovative companies. Unlike off-the-shelf processors, FPGAs, or even ASSPs, a full- or semi-custom ASIC is… Read More

In today’s data-driven systems—from cloud storage and AI accelerators to automotive logging and edge computing—every byte counts. The exponential growth in data volumes, real-time processing demands, and constrained bandwidth has made efficient, lossless data compression a mission-critical requirement. Software-based… Read More

Twenty years ago, Blue Pearl showcased its first-generation ASIC and FPGA static verification solution at the 2004 Design Automation Conference. If you are attending DAC 2024, stop by booth 1439 and see how 20 years of product development on the Visual Verification Suite has made chip design much more efficient.

The Visual Verification… Read More

Dieter Therssen obtained his master’s degree in Electronics Engineering from KU Leuven in 1987. He started his career as a hardware design engineer, using IMEC’s visionary tools and design methodologies in the early days of silicon integration.

Since then, Dieter developed his career across many digital technologies,… Read More

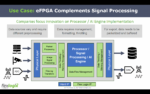

Field-Programmable Gate Arrays (FPGAs) have long been celebrated for their unmatched flexibility and programmability compared to Application-Specific Integrated Circuits (ASICs). And the introduction of Embedded FPGAs (eFPGAs) took these advantages to new heights. eFPGAs offer on-the-fly reconfiguration capabilities,… Read More

AI and ML techniques are popular topics, yet there are considerable challenges to those that want to design and build an AI accelerator for inferencing, as you need a team that understands how to model a neural network in a language like Python, turn that model into RTL, then verify that your RTL matches Python. Researchers from CERN,… Read More

In the ever-evolving world of Conversational AI and Automatic Speech Recognition (ASR), an upcoming LinkedIn Live webinar is set to redefine the speech-to-text industry. Achronix Semiconductor Corporation is teaming up with Myrtle.ai to bring you a webinar on October 24, 2023, at 8:30am PST.

Moderated by EE Times’ Sr. Reporter,… Read More

S2C, a leading provider of FPGA-based prototyping solutions, has helped a client achieve high-performance secure GPU chip verification. With the help of S2C’s Prodigy prototyping solution, the client was able to start software development and hardware-software co-design early, leading to accelerated time-to-market… Read More