If you are familiar with Processor IP core, you certainly know DesignWare ARC EM4 core, 32-bit CPU that SoC designers can optimize for a wide range of uses, and differentiate by using patented configuration technology to tailor each ARC core instance to meet specific performance, power and area requirements. If you develop a product addressing safety critical market, like Automotive or Medical, integrating a CPU core, you will need this processor to comply with ISO26262 standard. This means that the tool chain used to develop the processor has been audited and certified, the related safety documentation is available from Synopsys, and can be reused by the chip maker, and that the product itself is safety ready.

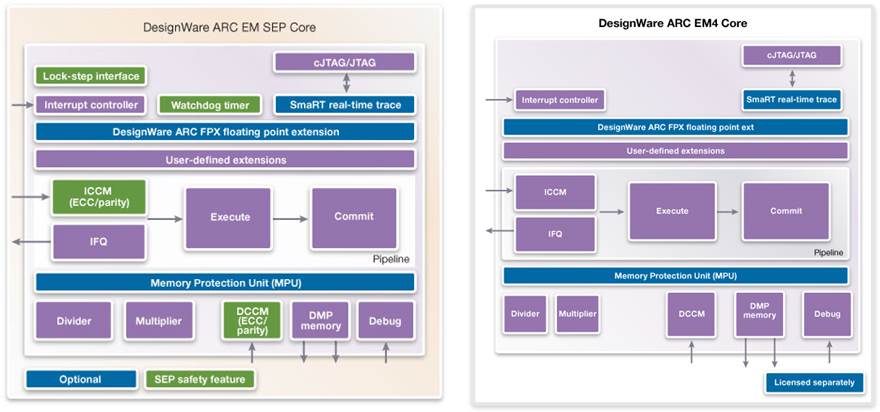

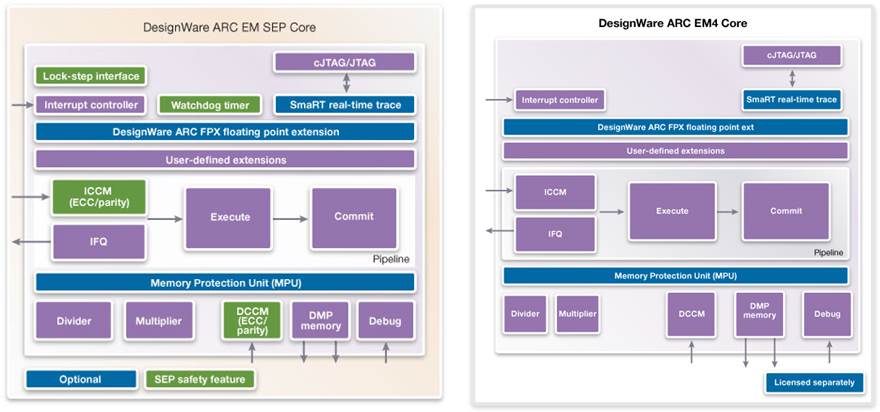

Let’s have a look at ARC EM SEP (Safety Enhancement Package) Core architecture, on the left side of the picture. If you compare it with ARC EM4 Core, on the right, you can immediately identify the safety related features: the blocks in green on the left, like Watchdog Timer, Lock-step interface or ICCM and DCCM where ECC/parity has been integrated.

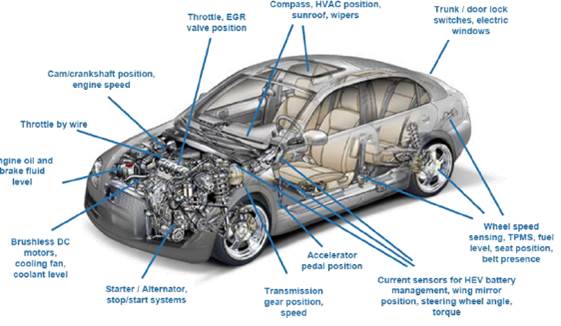

The Automotive market is moving faster than ever to integrate more electronic content, this is true for entertainment, when a passenger can feel like being in a plane, watching a movie during a long travel, and this is also true for certain safety critical function like ABS or Body Control. The trend in Automotive Electronic is to localize processing close to the sensors to perform specific function, rather than using a central CPU, performing all these functions (just take a look at the picture below). Thus, you need a small footprint but powerful IP processor like ARC EM SEP, offering performance up to 300 MHz and power consumption as low as 16 µW/MHz on typical 65-nanometer (nm) low power silicon processes. And you need a processor core with integrated hardware safety features, so you can comply with ISO26262, and address safety critical applications.

To summarize, ARC EM SEP allow building distributed intelligence applications, thanks to automotive specific features set:

- Optimized for high-efficiency, low-power embedded automotive applications

- Automotive Safety Integrity Level D (ASIL D)-ready DesignWare ARC MetaWare Compiler streamlines development of ISO 26262-compliant software

- Integrated safety features include parity support and error-correcting code (ECC) technology

- Detailed IP safety documentation eases certification of ARC EM SEP-based systems

Like with other cores from ARC family, Synopsys customers can differentiate by creating own instruction, and gain market share on such a competitive market. Safety critical features integrated into ARC EM SEP should allow targeting Medical applications, expected to strongly grow in the future.

More Articles by Eric Esteve …..

From Eric Esteve from IPnest

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.