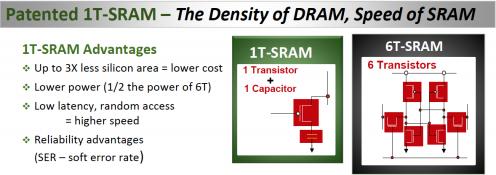

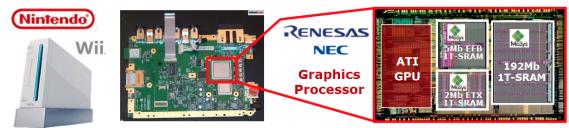

I’ve read about MoSys over the years and had the chance this week to interview Nani Subraminian, Engineering Manager about the types of EDA tools that they use and how design data management has been deployed to keep the design process organized. My background includes both DRAM and SRAM design, so I’ve been curious about how MoSys offers embedded DRAM as IP. They’ve basically made the DRAM look like an SRAM from an interface viewpoint (so no more RAS, CAS, OE complex timing).

Nani Subramanian, MoSys

Q: What does MoSys offer?

A: We enable high-speed chip to chip communications. Also we provide memory IP, and SerDes IP to IC designers.

Q: How long have you been with MoSys?

A: I was previously at Prism Circuits (where the SerDes circuit came from) then it was acquired by MoSys a few years ago.

Q: How many IC projects are there at MoSys today?

A: We have custom designers, ASIC design and SerDes design projects going on right now.

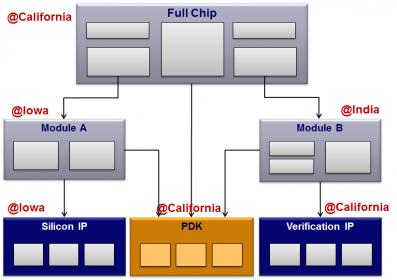

Q: Where are your designers located geographically?

A: We have multiple sites: Santa Clara, India, Iowa (SerDes IP).

Q: How did you decide to do IC design data management?

A: Because of our multi-site IC design process we needed design data management that worked inside of the Cadence Virtuoso Schematic and layout tools and it had to support multi-site (schematics in US, layout in India), so we chose the SOS tool from ClioSoft. We had evaluated other companies and decided on ClioSoft.

Q: What attracted you to SOS for design data management?

A: Many significant features. Some of them are the usage of low disk space using cache mechanism, multi site design support, reference project features and so on.

Q: Is there a learning curve with design data management?

A: Yes a small learning curve, at PRISM we had gotten used to the idea of check-in and check-out with SOS and Cadence Virtuoso layout tools. Our designers and layout people could learn the new usage quickly. Setting up multi-site was a CAD effort, not really a designer issue. We just chose one of our existing servers to install SOS on, no new hardware was required. All sites do both layout and schematics in Santa Clara and India.

Q: For SPICE circuit simulation which tools do you prefer to use?

A: Several. We’re using Spectre for our SPICE-level simulations on designs like PLL and other IP blocks. On larger mixed-signal designs we use UltraSim and HSIM because of the capacity. Finally, we’re using Berkeley DA simulator AFS to speed up HSPICE type jobs.

Q: How do you submit all of those SPICE jobs?

A: Our designers can run SPICE either on Linux boxes or on LSF servers.

Q: Which EDA tool is used for RTL simulation?

A: NC-Verilog from Cadence is used for RTL-level digital designs. Also we can run NC-Verilog along with UltraSim to get results on mixed-signal designs at both the RTL and transistor levels.

Q: How about DRC/LVS tools?

A: We use the Mentor tools, Calibre on LVS/DRC/DFM because they are the reference standard tools used at the foundries.

Q: Which foundries are you designing for?

A: TSMC is a major one, along with multiple others.

Q: Which extraction tools are you using?

A: Both StarRC and Calibre. For the highest accuracy blocks we use Raphael.

Q: Is EM and IR analysis important at MoSys?

A: Yes, and we’re using tools from Apache, now part of Ansys.

Q: In your digital logic how do you do Place & Route?

A: Another Cadence tool called First Encounter.

Q: When did you first start using IC design data management?

A: Four years now, both at Prism and now at MoSys.

Q: What are some of the benefits of DDM?

A: There’s a reference project feature in SOS where a chip may reference an IP block, that references another IP block. All the references are automated, so we maintain the IP data in our repository and can see any new updates to any IP. PDK data management is also put under version control with SOS, so as the foundry supplies us with different versions of a PDK we can see all the differences between PDKs. In 6.x version we are now using the Schematic Diff feature quite a bit, and we are getting ready to start using the hierarchical Schematic Diff.

Q: How is support at ClioSoft?

A: When we send an email question it gets answered pretty quickly, so it keeps us happy. Our local AE provides good support, especially to teach us new features that we are trying out for the first time.

Q: How does design data management help improve your time to market?

A: If a layout was LVS clean a week ago, and now it doesn’t pass LVS, then we can go back in time to see if anything has changed since then to make our design require new LVS runs. Did the rule deck change, or did my IC layout change? This capability really helps us to pinpoint the source of differences.

Q: Have you done any customization in your design flow?

A: Yes, we’re using an internally developed dashboard to show us the status of every critical block, and it gets updated by looking at the SOS database at any point in the entire design process. Our dashboard uses PHP and just accesses the SOS data.

Q: What states does an IC block go through?

A: Initial schematic, ready for IC layout, first IC layout, lvs clean, ready for extraction, post-layout qualified, final layout, final schematic. These states are all completely user-defined tags to tell us where in the design process each block is in.

Q: How many people at MoSys are using this design data management?

A: Between 50 to 75 people across all of our sites are users, it just depends on how many active projects we may be working on at the moment.

Q: What about CAD support from ClioSoft?

A: Our CAD people do the setup of the projects, and then designers can just use their tools. Migrating from 5.x to 6.x in ClioSoft there were some issues on what update meant, so we wrote some scripts to have the features we wanted.

Q: Are there any user groups for ClioSoft?

A: Not that we have attended, but that sounds like a good idea.

Summary

MoSys has grown into a public company based on expertise in embedding DRAM for IC designers and making the electrical interface easy to use, plus they offer SerDes and the new BandWidth Engine. Their EDA tool flow is a best-in-class approach with a mixture of tools from several vendors: Cadence, Mentor, Synopsys, ClioSoft and Berkeley DA. Keeping their IC data organized and synchronized is accomplished with design data management from ClioSoft.

To learn more about IC design data management consider attending the ClioSoft webinar (Manage Your Cadence Virtuoso Libraries, PDKs & Design IPs) on January 31.

Also Read

Hardware Configuration Management approach awarded a Patent

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.