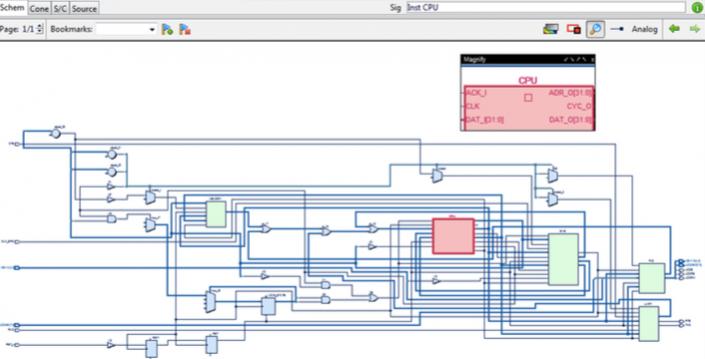

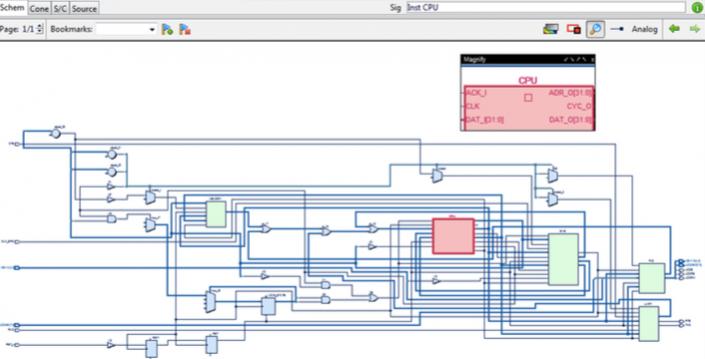

In the late 1990s I was the VP Engineering at Ambit Design Systems. We had a synthesis product (called BuildGates, nobody ever forgot the name). Both our own engineers and our customers wanted to be able to take a look at the gate-level netlist that was generated from their RTL. We used a product from a company called Concept Engineering based in Freiburg, as opposed to Munich where almost all other German EDA is centered. This would take the netlist, place all the inputs on the left, all the outputs on the right and then run a placement algorithm (probably pretty similar to P&R placement) on the netlist to decide where to put the gates and then run a router (probably pretty different from P&R routing) to put all the wires in with the idea of making the final result as pretty and readable as possible. This worked really well on moderate sized designs but since BuildGates could take 1M gate designs and synthesize them flat, it didn’t work too well on that sort of design—but then there is no good way to display a million gate netlist well.We had an OEM agreement with them to ship this product, now called NLview, to our customers. So, as it turns out did everyone in EDA who needed a schematic viewer (except Synopsys who needed it a decade earlier). That business still exists and whenever in EDA you see an automatically generated schematic that is probably what you are looking at. They then extended the technology so it was possible to look at hierarchical designs, Verilog, SystemVerilog, VHDL. Then transistor level designs in SPICE. Basically take pretty much any input and display it in a way that was both pretty (didn’t look like a rat’s nest) and effective for an engineer trying to follow his or her way around the design.

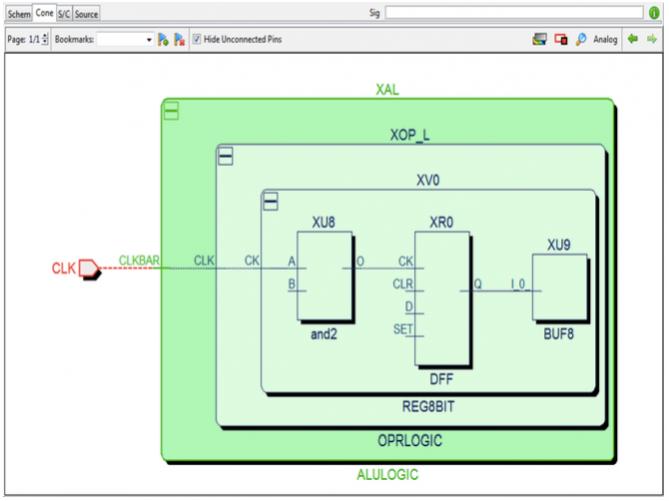

In the late 1990s I was the VP Engineering at Ambit Design Systems. We had a synthesis product (called BuildGates, nobody ever forgot the name). Both our own engineers and our customers wanted to be able to take a look at the gate-level netlist that was generated from their RTL. We used a product from a company called Concept Engineering based in Freiburg, as opposed to Munich where almost all other German EDA is centered. This would take the netlist, place all the inputs on the left, all the outputs on the right and then run a placement algorithm (probably pretty similar to P&R placement) on the netlist to decide where to put the gates and then run a router (probably pretty different from P&R routing) to put all the wires in with the idea of making the final result as pretty and readable as possible. This worked really well on moderate sized designs but since BuildGates could take 1M gate designs and synthesize them flat, it didn’t work too well on that sort of design—but then there is no good way to display a million gate netlist well.We had an OEM agreement with them to ship this product, now called NLview, to our customers. So, as it turns out did everyone in EDA who needed a schematic viewer (except Synopsys who needed it a decade earlier). That business still exists and whenever in EDA you see an automatically generated schematic that is probably what you are looking at. They then extended the technology so it was possible to look at hierarchical designs, Verilog, SystemVerilog, VHDL. Then transistor level designs in SPICE. Basically take pretty much any input and display it in a way that was both pretty (didn’t look like a rat’s nest) and effective for an engineer trying to follow his or her way around the design. It turns out that this is perfect for the modern design style that is largely assembling IP blocks. One problem with most IP blocks is that they come from another part of the company or from a 3rd party. No matter what the format, the block can be displayed in a way that makes it easy for an engineer to move around the design, up and down the hierarchy and so on, to get an understanding of the block. Paths can be traced, drawn in different colors and so on. There is full cross-probing between the graphical display and the input and the levels of the hierarchy.But they went further and added a lot of debug features to create a product called StarVision Pro that makes debugging a design a lot easier than starting from just the opaque input file. Cones from inputs or specific pins can be traced, critical paths can be excised from a netlist and written out in SPICE for detailed simulation and a lot more capabilities that an engineer trying to understand and debug an IP block requires.There is a lot of capability for analyzing the clock, highlighting the clock trees and highlighting all the domain crossings from one clock to another.

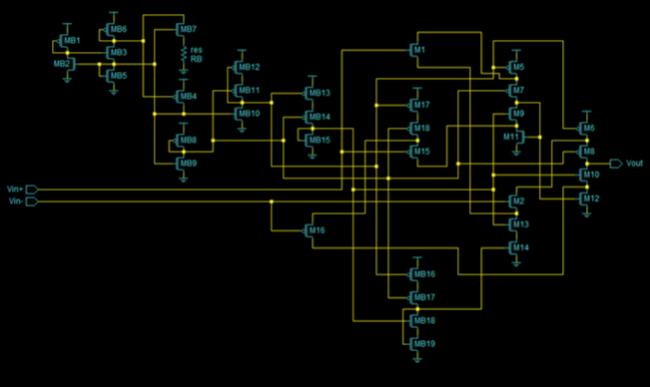

It turns out that this is perfect for the modern design style that is largely assembling IP blocks. One problem with most IP blocks is that they come from another part of the company or from a 3rd party. No matter what the format, the block can be displayed in a way that makes it easy for an engineer to move around the design, up and down the hierarchy and so on, to get an understanding of the block. Paths can be traced, drawn in different colors and so on. There is full cross-probing between the graphical display and the input and the levels of the hierarchy.But they went further and added a lot of debug features to create a product called StarVision Pro that makes debugging a design a lot easier than starting from just the opaque input file. Cones from inputs or specific pins can be traced, critical paths can be excised from a netlist and written out in SPICE for detailed simulation and a lot more capabilities that an engineer trying to understand and debug an IP block requires.There is a lot of capability for analyzing the clock, highlighting the clock trees and highlighting all the domain crossings from one clock to another. At the transistor level, where the netlist can be incredibly complex due to parasitics, there are features to prune the netlist, merge capacitance and resistance when they are small, automatic recognition of gates from transistor structures and even creating hierarchy out of flat netlists. Basically, they can read in a transistor-level netlist and make it a lot more intelligible to the designer without losing accuracy. Moderately large blocks can be read straight in fast, huge blocks can be pre-processed into a binary format in an overnight batch mode and then the binary loads almost instantaneously.

At the transistor level, where the netlist can be incredibly complex due to parasitics, there are features to prune the netlist, merge capacitance and resistance when they are small, automatic recognition of gates from transistor structures and even creating hierarchy out of flat netlists. Basically, they can read in a transistor-level netlist and make it a lot more intelligible to the designer without losing accuracy. Moderately large blocks can be read straight in fast, huge blocks can be pre-processed into a binary format in an overnight batch mode and then the binary loads almost instantaneously.

Sponsor

Instance

Array

(

[node_name] => Concept Engineering

[node_id] => Array

(

[0] => 2

)

)

Instance

Array

(

[node_name] =>

[node_id] => Array

(

[0] => 2

)

[title] => Recent Forum Threads

)

Threads

XF\Mvc\Entity\ArrayCollection Object

(

[entities:protected] => Array

(

[24868] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 57

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24868

[node_id] => 2

[title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[reply_count] => 31

[view_count] => 2855

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775054550

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98833

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1775508769

[last_post_id] => 98986

[last_post_user_id] => 35301

[last_post_username] => Xebec

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15457

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775498647

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 104

[alerts_unread] => 104

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9343

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24890] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 61

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24890

[node_id] => 2

[title] => Bernie Sanders has a plan to stop the AI industry

[reply_count] => 0

[view_count] => 31

[user_id] => 396

[username] => swka

[post_date] => 1775506549

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98985

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775506549

[last_post_id] => 98985

[last_post_user_id] => 396

[last_post_username] => swka

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 58

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 396

[username] => swka

[username_date] => 0

[username_date_visible] => 0

[email] => swka@hotmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 177

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1294249501

[last_activity] => 1775505522

[last_summary_email_date] => 1686406808

[trophy_points] => 43

[alerts_unviewed] => 6

[alerts_unread] => 6

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 152

[warning_points] => 0

[is_staff] => 0

[secret_key] => OO7IirVdCg0w0g8RomEV2hwUwfXsJgMD

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24854] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 65

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24854

[node_id] => 2

[title] => Nvidia invests $2B so that Marvell (and its XPU Customers) to adopt "NVLink Fusion"

[reply_count] => 10

[view_count] => 1438

[user_id] => 90385

[username] => NY_Sam2

[post_date] => 1774968242

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98788

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":1,"3":1}

[last_post_date] => 1775504855

[last_post_id] => 98984

[last_post_user_id] => 1305

[last_post_username] => KevinK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 62

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 90385

[username] => NY_Sam2

[username_date] => 0

[username_date_visible] => 0

[email] => petekennedy1989@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/New_York

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 37

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1642621712

[last_activity] => 1775348595

[last_summary_email_date] => 1767709207

[trophy_points] => 18

[alerts_unviewed] => 16

[alerts_unread] => 16

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 55

[warning_points] => 0

[is_staff] => 0

[secret_key] => egi-LmWHpsbQRZ7Y0Lk56hMyhUsrDhDE

[privacy_policy_accepted] => 1642621712

[terms_accepted] => 1642621712

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24885] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 69

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24885

[node_id] => 2

[title] => Intel CEO embraces its 18A node for external customers as 18A-P gets 'inbound interest' — company cites increasing yields

[reply_count] => 7

[view_count] => 902

[user_id] => 5185

[username] => Fred Chen

[post_date] => 1775354521

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98939

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":2}

[last_post_date] => 1775498100

[last_post_id] => 98982

[last_post_user_id] => 326256

[last_post_username] => Artificer60

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 66

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5185

[username] => Fred Chen

[username_date] => 0

[username_date_visible] => 0

[email] => chen.t.fred@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 4

[secondary_group_ids] =>

[display_style_group_id] => 4

[permission_combination_id] => 92

[message_count] => 2596

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1333032401

[last_activity] => 1775496121

[last_summary_email_date] => 1605940563

[trophy_points] => 113

[alerts_unviewed] => 1

[alerts_unread] => 1

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1888

[warning_points] => 0

[is_staff] => 0

[secret_key] => 5m-bZq0HRSi9VA-96QONHJeevdQas5S8

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24881] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 73

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24881

[node_id] => 2

[title] => Samsung and SK are expanding fast, but why is memory still in short supply?

[reply_count] => 15

[view_count] => 983

[user_id] => 5185

[username] => Fred Chen

[post_date] => 1775280977

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98907

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1775490999

[last_post_id] => 98981

[last_post_user_id] => 35301

[last_post_username] => Xebec

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 66

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5185

[username] => Fred Chen

[username_date] => 0

[username_date_visible] => 0

[email] => chen.t.fred@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 4

[secondary_group_ids] =>

[display_style_group_id] => 4

[permission_combination_id] => 92

[message_count] => 2596

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1333032401

[last_activity] => 1775496121

[last_summary_email_date] => 1605940563

[trophy_points] => 113

[alerts_unviewed] => 1

[alerts_unread] => 1

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1888

[warning_points] => 0

[is_staff] => 0

[secret_key] => 5m-bZq0HRSi9VA-96QONHJeevdQas5S8

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24874] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 77

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24874

[node_id] => 2

[title] => Seligman Ventures Leads Cognichip’s $60M Series A to Back Physics-Informed AI for Chip Design, Intel CEO Lip-Bu Tan and Seligman Ventures’ Umesh Padva

[reply_count] => 14

[view_count] => 908

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775133323

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98862

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775485967

[last_post_id] => 98979

[last_post_user_id] => 38697

[last_post_username] => blueone

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15457

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775498647

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 104

[alerts_unread] => 104

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9343

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24889] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 81

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24889

[node_id] => 2

[title] => The Quantum Foundry: Google Including Neutral Atom Qubit Approach

[reply_count] => 0

[view_count] => 126

[user_id] => 19450

[username] => user nl

[post_date] => 1775454771

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98968

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775454771

[last_post_id] => 98968

[last_post_user_id] => 19450

[last_post_username] => user nl

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 78

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 19450

[username] => user nl

[username_date] => 0

[username_date_visible] => 0

[email] => mauricehmjanssen@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 1

[style_variation] =>

[timezone] => Europe/Amsterdam

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 538

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1424291496

[last_activity] => 1775500397

[last_summary_email_date] =>

[trophy_points] => 63

[alerts_unviewed] => 0

[alerts_unread] => 1

[avatar_date] => 1726169369

[avatar_width] => 384

[avatar_height] => 384

[avatar_highdpi] => 1

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 392

[warning_points] => 0

[is_staff] => 0

[secret_key] => V-1lb5_AW69yhzqA5ok9b64U0fMjJiqf

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24888] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 85

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24888

[node_id] => 2

[title] => Governing the 1.8 Tb/s Reality Gap: EM Corridors, Power Architectures, and Agentic AI

[reply_count] => 1

[view_count] => 134

[user_id] => 444140

[username] => moh.kolb

[post_date] => 1775431131

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98963

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775431215

[last_post_id] => 98964

[last_post_user_id] => 444140

[last_post_username] => moh.kolb

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 82

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 444140

[username] => moh.kolb

[username_date] => 0

[username_date_visible] => 0

[email] => moh@kolbehdari.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Phoenix

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 6

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1775069311

[last_activity] => 1775495037

[last_summary_email_date] => 1775069311

[trophy_points] => 1

[alerts_unviewed] => 1

[alerts_unread] => 1

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 0

[warning_points] => 0

[is_staff] => 0

[secret_key] => EG539H6nqaiPLLZ4UXYEvAY-Py_6iJOA

[privacy_policy_accepted] => 1775069311

[terms_accepted] => 1775069311

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24887] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 89

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24887

[node_id] => 2

[title] => Trump administration proposes expanding Chinese tech gear crackdown

[reply_count] => 1

[view_count] => 229

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775407729

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98957

[first_post_reaction_score] => 0

[first_post_reactions] => {"4":1}

[last_post_date] => 1775408597

[last_post_id] => 98959

[last_post_user_id] => 20231

[last_post_username] => Barnsley

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15457

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775498647

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 104

[alerts_unread] => 104

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9343

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24818] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 93

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24818

[node_id] => 2

[title] => SK Hynix to buy $8 billion in ASML chipmaking tools in largest disclosed order

[reply_count] => 3

[view_count] => 1972

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1774365161

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98632

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775407116

[last_post_id] => 98956

[last_post_user_id] => 5185

[last_post_username] => Fred Chen

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15457

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775498647

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 104

[alerts_unread] => 104

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9343

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8503

[message_count] => 62233

[last_post_id] => 98986

[last_post_date] => 1775508769

[last_post_user_id] => 35301

[last_post_username] => Xebec

[last_thread_id] => 24868

[last_thread_title] => Intel to Repurchase 49% Equity Interest in Ireland Fab Joint Venture

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24886] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 97

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24886

[node_id] => 2

[title] => A thought experiment - "What if everything still ran on vacuum tubes?"

[reply_count] => 0

[view_count] => 210

[user_id] => 35301

[username] => Xebec

[post_date] => 1775401011

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98950

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775401011

[last_post_id] => 98950

[last_post_user_id] => 35301

[last_post_username] => Xebec

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default