You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The Design Automation Conference has been the pinnacle for semiconductor design for almost 60 years. This year will be my 38th DAC and I can’t wait to see everyone again. One of the companies I will be spending time with this year is Altair.

Last month Altair acquired our friends at Concept Engineering, the leading provider… Read More

Webinars have been a popular form of communication since even before SemiWiki existed and they are a mainstay in today’s fast-moving semiconductor ecosystem.

In the past, SemiWiki has assisted with more than a hundred webinars. Today SemiWiki can do a complete webinar from start to finish using the GotoWebinar software. SemiWiki… Read More

An SoC can have a collection of multiple blocks and IPs from different sources integrated together along with several other analog and digital components within a native environment. The IPs can be at different levels of abstractions; their RTL descriptions can be in different languages such as Verilog, VHDL, or SystemVerilog.… Read More

OEM agreements don’t seem to work in EDA. Sometimes they are signed but usually they turn out to be closer to joint marketing agreements. The reason seems to be that EDA software is complex and requires high-touch support especially when getting the product first installed and introduced into a production flow. The effect… Read More

SoC design these days is largely about assembling externally developed semiconductor IP with a small amount of differentiated content. Only companies who have to adopt new processes instantly develop a lot of their own IP. It makes more sense to license it. Partially because there is not a lot of differentiation in standards-based… Read More

This year is most notably the 50th anniversary of Moore’s Law. It is also the 25th anniversary of Concept Engineering. They were founded in 1990 in Freiburg Germany. They started by providing automatic schematic generation from netlist. They sold primarily to other EDA companies and to internal development groups in semiconductor… Read More

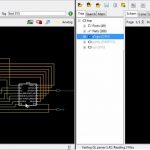

During SNUG I took the opportunity to chat to Choon-Hoe Yeoh of Lattice Semiconductor about how they use Concept Engineering’s Starvision Pro product. He is the senior director of EDA tools and methodologies there.

Lattice Semiconductor is a manufacturer of low-power, small-footprint, low-cost programmable logic devices.… Read More

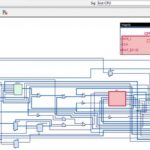

Starvision Pro from Concept Engineering is a bit like one of those Leatherman multi-tools, it has a huge number of different functions, some of them fairly specialized but nonetheless incredibly useful. Many of these functions are unique to Starvision Pro, with nothing else like it on the market. Some new videos, produced by EDA… Read More

In the late 1990s I was the VP Engineering at Ambit Design Systems. We had a synthesis product (called BuildGates, nobody ever forgot the name). Both our own engineers and our customers wanted to be able to take a look at the gate-level netlist that was generated from their RTL. We used a product from a company called Concept Engineering… Read More

In today’s SoC world where multiple analog and digital blocks along with IPs at different levels of abstractions are placed together on a single chip, debugging at all levels becomes quite difficult and clumsy. While one is working at the top level and needs to investigate a particular connection at an intermediate hierarchical… Read More