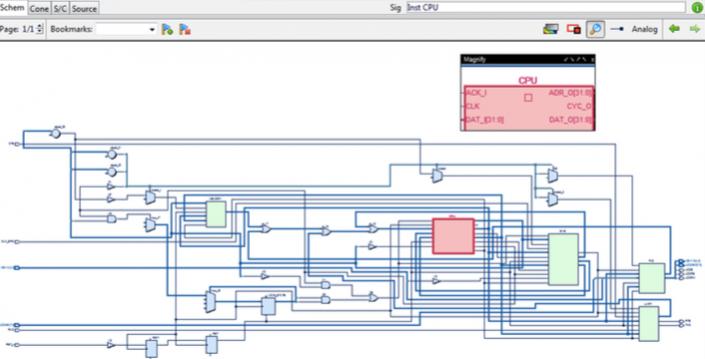

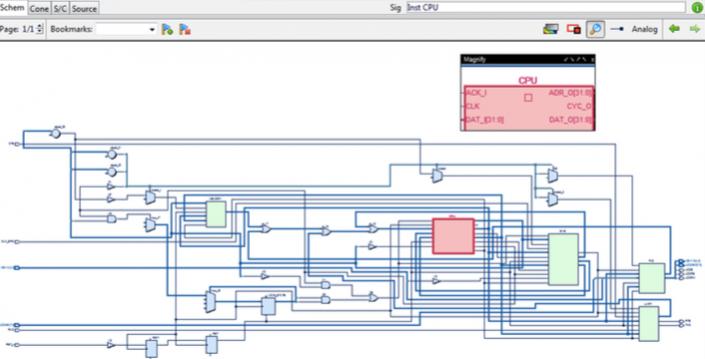

In the late 1990s I was the VP Engineering at Ambit Design Systems. We had a synthesis product (called BuildGates, nobody ever forgot the name). Both our own engineers and our customers wanted to be able to take a look at the gate-level netlist that was generated from their RTL. We used a product from a company called Concept Engineering based in Freiburg, as opposed to Munich where almost all other German EDA is centered. This would take the netlist, place all the inputs on the left, all the outputs on the right and then run a placement algorithm (probably pretty similar to P&R placement) on the netlist to decide where to put the gates and then run a router (probably pretty different from P&R routing) to put all the wires in with the idea of making the final result as pretty and readable as possible. This worked really well on moderate sized designs but since BuildGates could take 1M gate designs and synthesize them flat, it didn’t work too well on that sort of design—but then there is no good way to display a million gate netlist well.We had an OEM agreement with them to ship this product, now called NLview, to our customers. So, as it turns out did everyone in EDA who needed a schematic viewer (except Synopsys who needed it a decade earlier). That business still exists and whenever in EDA you see an automatically generated schematic that is probably what you are looking at. They then extended the technology so it was possible to look at hierarchical designs, Verilog, SystemVerilog, VHDL. Then transistor level designs in SPICE. Basically take pretty much any input and display it in a way that was both pretty (didn’t look like a rat’s nest) and effective for an engineer trying to follow his or her way around the design.

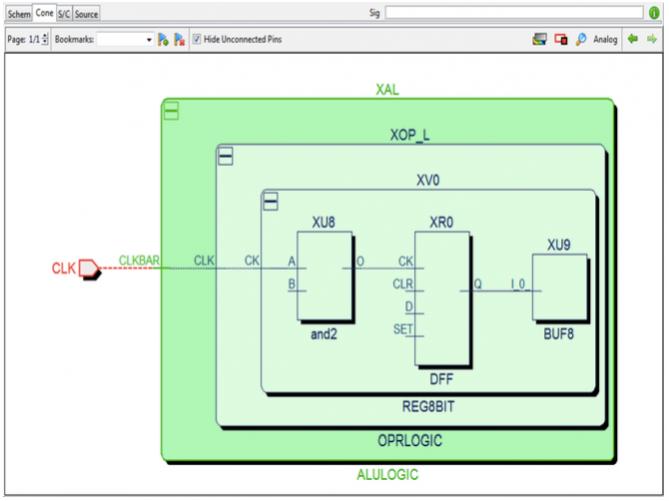

In the late 1990s I was the VP Engineering at Ambit Design Systems. We had a synthesis product (called BuildGates, nobody ever forgot the name). Both our own engineers and our customers wanted to be able to take a look at the gate-level netlist that was generated from their RTL. We used a product from a company called Concept Engineering based in Freiburg, as opposed to Munich where almost all other German EDA is centered. This would take the netlist, place all the inputs on the left, all the outputs on the right and then run a placement algorithm (probably pretty similar to P&R placement) on the netlist to decide where to put the gates and then run a router (probably pretty different from P&R routing) to put all the wires in with the idea of making the final result as pretty and readable as possible. This worked really well on moderate sized designs but since BuildGates could take 1M gate designs and synthesize them flat, it didn’t work too well on that sort of design—but then there is no good way to display a million gate netlist well.We had an OEM agreement with them to ship this product, now called NLview, to our customers. So, as it turns out did everyone in EDA who needed a schematic viewer (except Synopsys who needed it a decade earlier). That business still exists and whenever in EDA you see an automatically generated schematic that is probably what you are looking at. They then extended the technology so it was possible to look at hierarchical designs, Verilog, SystemVerilog, VHDL. Then transistor level designs in SPICE. Basically take pretty much any input and display it in a way that was both pretty (didn’t look like a rat’s nest) and effective for an engineer trying to follow his or her way around the design. It turns out that this is perfect for the modern design style that is largely assembling IP blocks. One problem with most IP blocks is that they come from another part of the company or from a 3rd party. No matter what the format, the block can be displayed in a way that makes it easy for an engineer to move around the design, up and down the hierarchy and so on, to get an understanding of the block. Paths can be traced, drawn in different colors and so on. There is full cross-probing between the graphical display and the input and the levels of the hierarchy.But they went further and added a lot of debug features to create a product called StarVision Pro that makes debugging a design a lot easier than starting from just the opaque input file. Cones from inputs or specific pins can be traced, critical paths can be excised from a netlist and written out in SPICE for detailed simulation and a lot more capabilities that an engineer trying to understand and debug an IP block requires.There is a lot of capability for analyzing the clock, highlighting the clock trees and highlighting all the domain crossings from one clock to another.

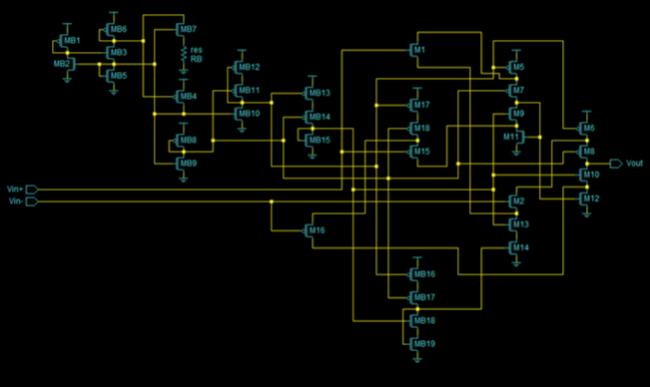

It turns out that this is perfect for the modern design style that is largely assembling IP blocks. One problem with most IP blocks is that they come from another part of the company or from a 3rd party. No matter what the format, the block can be displayed in a way that makes it easy for an engineer to move around the design, up and down the hierarchy and so on, to get an understanding of the block. Paths can be traced, drawn in different colors and so on. There is full cross-probing between the graphical display and the input and the levels of the hierarchy.But they went further and added a lot of debug features to create a product called StarVision Pro that makes debugging a design a lot easier than starting from just the opaque input file. Cones from inputs or specific pins can be traced, critical paths can be excised from a netlist and written out in SPICE for detailed simulation and a lot more capabilities that an engineer trying to understand and debug an IP block requires.There is a lot of capability for analyzing the clock, highlighting the clock trees and highlighting all the domain crossings from one clock to another. At the transistor level, where the netlist can be incredibly complex due to parasitics, there are features to prune the netlist, merge capacitance and resistance when they are small, automatic recognition of gates from transistor structures and even creating hierarchy out of flat netlists. Basically, they can read in a transistor-level netlist and make it a lot more intelligible to the designer without losing accuracy. Moderately large blocks can be read straight in fast, huge blocks can be pre-processed into a binary format in an overnight batch mode and then the binary loads almost instantaneously.

At the transistor level, where the netlist can be incredibly complex due to parasitics, there are features to prune the netlist, merge capacitance and resistance when they are small, automatic recognition of gates from transistor structures and even creating hierarchy out of flat netlists. Basically, they can read in a transistor-level netlist and make it a lot more intelligible to the designer without losing accuracy. Moderately large blocks can be read straight in fast, huge blocks can be pre-processed into a binary format in an overnight batch mode and then the binary loads almost instantaneously.

Sponsor

Instance

Array

(

[node_name] => Concept Engineering

[node_id] => Array

(

[0] => 2

)

)

Instance

Array

(

[node_name] =>

[node_id] => Array

(

[0] => 2

)

[title] => Recent Forum Threads

)

Threads

XF\Mvc\Entity\ArrayCollection Object

(

[entities:protected] => Array

(

[25076] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 57

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25076

[node_id] => 2

[title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[reply_count] => 18

[view_count] => 1685

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1778548540

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99798

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1778990340

[last_post_id] => 99967

[last_post_user_id] => 14042

[last_post_username] => hist78

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15567

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1778952105

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 78

[alerts_unread] => 78

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9444

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25109] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 61

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25109

[node_id] => 2

[title] => World’s first native color LiDAR gives machines human-like vision

[reply_count] => 2

[view_count] => 331

[user_id] => 14042

[username] => hist78

[post_date] => 1778879963

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99936

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1778989241

[last_post_id] => 99966

[last_post_user_id] => 14042

[last_post_username] => hist78

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 58

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 14042

[username] => hist78

[username_date] => 0

[username_date_visible] => 0

[email] => ckckhcdc@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 0

[activity_visible] => 0

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 4333

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1389969050

[last_activity] => 1778958496

[last_summary_email_date] => 1605978520

[trophy_points] => 113

[alerts_unviewed] => 0

[alerts_unread] => 1

[avatar_date] => 1604959511

[avatar_width] => 807

[avatar_height] => 384

[avatar_highdpi] => 1

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 4202

[warning_points] => 0

[is_staff] => 0

[secret_key] => 2YRSnPrl4fVQSdv3R6uqHxqi6BDQOXve

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25017] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 65

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25017

[node_id] => 2

[title] => Industry faces “acute” CPU shortage with hope that Intel 18A yields improve

[reply_count] => 48

[view_count] => 8446

[user_id] => 5185

[username] => Fred Chen

[post_date] => 1777451029

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99529

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":2}

[last_post_date] => 1778965503

[last_post_id] => 99964

[last_post_user_id] => 334389

[last_post_username] => OneEng

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 62

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5185

[username] => Fred Chen

[username_date] => 0

[username_date_visible] => 0

[email] => chen.t.fred@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 4

[secondary_group_ids] =>

[display_style_group_id] => 4

[permission_combination_id] => 92

[message_count] => 2641

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1333032401

[last_activity] => 1778944993

[last_summary_email_date] => 1605940563

[trophy_points] => 113

[alerts_unviewed] => 1

[alerts_unread] => 1

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1939

[warning_points] => 0

[is_staff] => 0

[secret_key] => 5m-bZq0HRSi9VA-96QONHJeevdQas5S8

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25106] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 69

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25106

[node_id] => 2

[title] => Ming-Chi Kuo on Apple-Intel partnership, with TSMC lurking in the back

[reply_count] => 17

[view_count] => 1372

[user_id] => 90385

[username] => NY_Sam2

[post_date] => 1778794142

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99917

[first_post_reaction_score] => 3

[first_post_reactions] => {"1":3}

[last_post_date] => 1778960046

[last_post_id] => 99962

[last_post_user_id] => 334126

[last_post_username] => DepthFirst

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 66

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 90385

[username] => NY_Sam2

[username_date] => 0

[username_date_visible] => 0

[email] => petekennedy1989@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/New_York

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 50

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1642621712

[last_activity] => 1778794142

[last_summary_email_date] => 1767709207

[trophy_points] => 18

[alerts_unviewed] => 19

[alerts_unread] => 19

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 75

[warning_points] => 0

[is_staff] => 0

[secret_key] => egi-LmWHpsbQRZ7Y0Lk56hMyhUsrDhDE

[privacy_policy_accepted] => 1642621712

[terms_accepted] => 1642621712

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25074] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 73

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25074

[node_id] => 2

[title] => Cerebras to raise IPO price range to $150-$160 as demand surges, sources say

[reply_count] => 30

[view_count] => 2460

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1778511949

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99783

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":2}

[last_post_date] => 1778956720

[last_post_id] => 99961

[last_post_user_id] => 38697

[last_post_username] => blueone

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15567

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1778952105

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 78

[alerts_unread] => 78

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9444

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25098] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 77

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25098

[node_id] => 2

[title] => Trump lands in China for Xi summit with Nvidia CEO in tow

[reply_count] => 7

[view_count] => 1073

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1778684918

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99878

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1778956247

[last_post_id] => 99960

[last_post_user_id] => 35301

[last_post_username] => Xebec

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15567

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1778952105

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 78

[alerts_unread] => 78

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9444

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25108] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 81

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25108

[node_id] => 2

[title] => Chinese memory module makers ramp up production as CXMT DDR5 breakthrough hits market

[reply_count] => 1

[view_count] => 418

[user_id] => 5185

[username] => Fred Chen

[post_date] => 1778848947

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99927

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1778850209

[last_post_id] => 99928

[last_post_user_id] => 35301

[last_post_username] => Xebec

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 62

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5185

[username] => Fred Chen

[username_date] => 0

[username_date_visible] => 0

[email] => chen.t.fred@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 4

[secondary_group_ids] =>

[display_style_group_id] => 4

[permission_combination_id] => 92

[message_count] => 2641

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1333032401

[last_activity] => 1778944993

[last_summary_email_date] => 1605940563

[trophy_points] => 113

[alerts_unviewed] => 1

[alerts_unread] => 1

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1939

[warning_points] => 0

[is_staff] => 0

[secret_key] => 5m-bZq0HRSi9VA-96QONHJeevdQas5S8

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25107] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 85

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25107

[node_id] => 2

[title] => Exclusive: Inside MediaTek's Push to Lock Up T-Glass Supply — The Risks Behind Google's TPU Deal

[reply_count] => 0

[view_count] => 378

[user_id] => 398583

[username] => karin623

[post_date] => 1778831217

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99925

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1778831217

[last_post_id] => 99925

[last_post_user_id] => 398583

[last_post_username] => karin623

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 82

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 398583

[username] => karin623

[username_date] => 0

[username_date_visible] => 0

[email] => karin623@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => Asia/Hong_Kong

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 47

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1748753435

[last_activity] => 1778831217

[last_summary_email_date] => 1771856462

[trophy_points] => 18

[alerts_unviewed] => 4

[alerts_unread] => 4

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 66

[warning_points] => 0

[is_staff] => 0

[secret_key] => PBnrLVmUtkEL7YUKL8Ij_6L3tfKYRzDQ

[privacy_policy_accepted] => 1748753435

[terms_accepted] => 1748753435

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25101] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 89

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25101

[node_id] => 2

[title] => Is AI the "automobile" of this generation?

[reply_count] => 5

[view_count] => 477

[user_id] => 20231

[username] => Barnsley

[post_date] => 1778735519

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99897

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1778810558

[last_post_id] => 99922

[last_post_user_id] => 20231

[last_post_username] => Barnsley

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 86

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 20231

[username] => Barnsley

[username_date] => 0

[username_date_visible] => 0

[email] => apickering72@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => Asia/Irkutsk

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 1473

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1429440429

[last_activity] => 1778925738

[last_summary_email_date] => 1653315673

[trophy_points] => 113

[alerts_unviewed] => 13

[alerts_unread] => 13

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 768

[warning_points] => 0

[is_staff] => 0

[secret_key] => iAnkz9GTDfivRmH1BOp6OTrgESJR57G8

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25102] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 93

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25102

[node_id] => 2

[title] => TSMC wins major modem chip order from Apple

[reply_count] => 2

[view_count] => 770

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1778740690

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99898

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1778807849

[last_post_id] => 99920

[last_post_user_id] => 443721

[last_post_username] => rinoali

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15567

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1778952105

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 78

[alerts_unread] => 78

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9444

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8624

[message_count] => 63096

[last_post_id] => 99967

[last_post_date] => 1778990340

[last_post_user_id] => 14042

[last_post_username] => hist78

[last_thread_id] => 25076

[last_thread_title] => Intel’s stock tripled under Lip-Bu Tan. He still has not told most employees the plan.

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[25104] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 97

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 25104

[node_id] => 2

[title] => UMC Announces Release of 14nm eHV FinFET Platform, Advancing Innovation in Next-Generation Smartphone Displays

[reply_count] => 8

[view_count] => 552

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1778769169

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99904

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1778782352

[last_post_id] => 99915

[last_post_user_id] => 138292

[last_post_username] => MKWVentures

[prefix_id] => 0

[tags] => []

[custom_fields] => []