You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

SMACD 2026by Admin on 01-07-2026 at 3:03 am

Welcome to SMACD 2026

International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Applications to Circuit Design

REGISTER HERE… Read More

I’ve talked before about how Defacto provides a platform for scripted RTL assembly. Kind of a rethink of the IP-XACT concept but without need to get into XML (it works directly with SV), and with a more relaxed approach in which you decide what you want to automate and how you want to script it.

They’re hosting a webinar on May 28th 10-11am… Read More

Synopsys recently unleashed Fusion Compiler™, a new RTL-to-GDSII product that enables a data-driven design implementation by revamping Design Compiler architecture and leveraging the successful Fusion Technology –seamlessly fusing the logical and physical realms to produce predictable QoR. It is a long-awaited… Read More

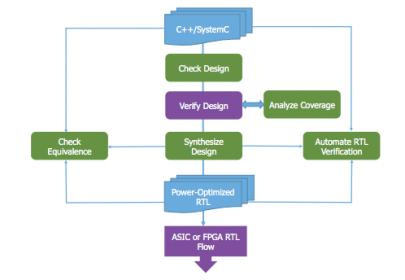

I’m on a mini-roll on the subject of high-level design for ML-based systems. No complaints from me, this is one of my favorite domains and is certainly a hot area; it’s great to that EDA vendors are so active in advancing ML-based design. Here I want to talk about the Catapult HLS flow for use in ML design.

Since I’ve covered the ML topic… Read More

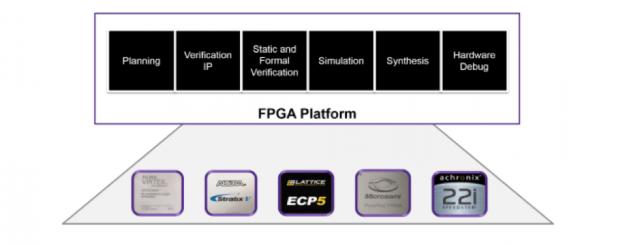

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More

This is part II of an article covering NetSpeed’s network-on-chip (NoC) offerings. This article dives a little deeper into what a NoC is and how NetSpeed’s network synthesis tool, NocStudio, helps system architects optimize a NoC for their system-on-a-chip (SoC) design.

Traditionally IC designers have used proprietary buses,… Read More

A couple of weeks back I wrote an article about the use of machine learning and deep neural networks in self-driving cars. Now I find that machine learning is also being applied to help build advanced end-to-end QoS (quality of service) solutions for the automotive IC market. With the advent of self-driving cars comes requirements… Read More

Teams buy HDL simulation for best bang for the buck. Teams buy hardware emulation for the speed. We’ve talked previously about SCE-MI transactors as a standardized vehicle to connect the two approaches to get the benefits of both in an accelerated testbench – what else should be accounted for?… Read More

In early 2000s, semiconductor design at RTL level was gaining momentum. The idea was to process more design steps such as insertion of test and other design structures upfront at the RTL level. The design optimization and verification were to be done at the RTL level to reduce long iterations through gate level design because changes… Read More

Hardware emulators and FPGA-based prototyping systems are descendants of the same ancestor. The Quickturn Systems Rapid Prototype Machine (RPM) introduced in May 1988 brought an array of Xilinx XC3090 FPGAs to emulate designs with hundreds of thousands of gates. From there, hardware emulators and FPGA-based prototyping … Read More