You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

When looking at the time to design and verify an SoC we’ve known for many years now that the verification effort requires more time than the design process. So anything that will shorten the verification effort will have the biggest impact on keeping your project on schedule.

A second trend is the amount of Analog content in… Read More

If you’re involved with AMS or transistor-level IC design then having visual tools will help you design and debug quicker. At DAC I met with Gerhard Angst, President and Founder of Concept Engineering to get an update.

Gerhard Angst (center), Concept Engineering… Read More

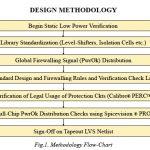

IC designer Shubhyant Chaturvediof AMD used EDA tools from Mentor Graphicsand Concept Engineeringto perform static, low-power verification of a mixed-signal SoC design with a combined CPU and GPU. Shubhyant presented a poster session at DAC two weeks ago in Austin, and I wanted to share it with my readers here at SemiWiki.… Read More

I’m utterly amazed at how IC-based products are improving our quality of life by implantable devices. The modern day pacemaker has given people added years of life by electrically stimulating the heart. A privately-held company called NeuroPace was founded in Mountain View, California to treat epilepsy by using responsive… Read More

Debugging an IC design at the transistor, Gate and RTL levels is often necessary to meet timing requirements and understand analog or digital behavior, yet the process itself can be a tedious one, filled with manual steps, therefore making it an error-prone process. EDA tools have been created to help us graphically debug transistor,… Read More

My background is IC design engineering, so it’s always a delight to talk with another engineer on their chip challenges. Today I spoke by phone with Sucharita Biswas, a Senior Hardware Engineer at Altera involved in IC test debug for FPGA devices.

… Read More

In EDA we often talk about how fast a SPICE circuit simulator is, or about capacity and accuracy compared to silicon measurements. Yes, speed, capacity and accuracy are important, however when talking to actual transistor-level circuit designers you discover something quite different, most of their time is spent doing debugging,… Read More

My first job out of college was doing transistor-level circuit design, so I’m always curious about how companies are doing billion-transistor chip design and debug these days at the FPGA companies.

I spoke with Yaron Kretchmer,he works at Altera and manages the engineering infrastructure group where they have a compute… Read More

With an HDL-based design methodology many IC engineers code in text languages like SystemVerilog and VHDL, so it’s only natural to use a text-based debug methodology. The expression that, “A picture is worth a thousand words” comes to my mind and in this case a visual debug approach is worth considering for … Read More

I first heard about SPICE Vision Pro when working at Mentor Graphics where we needed a way to visualize SPICE netlists and debug SPICE simulation results node by node on a design where we didn’t have the original schematics. Last Monday I met the engineers from Concept Engineering in their booth at DAC to get an update, Gerhard… Read More