Digital designers have used logic optimization and logic synthesis for decades as a means to produce more optimal designs with EDA tools. On the analog and transistor-level side of design the efforts to automatically optimize for speed or power have generally been limited to circuits with only a handful of transistors. These automated transistor-level optimizations have been improving quite a bit over the past decade, and I attended a webinar today about full-custom, low-power design methodology. The webinar presenter was Michael Pronath. He earned his PhD in Electronics at the Technische Universität München and has worked the past 12 years at MunEDA in Germany.

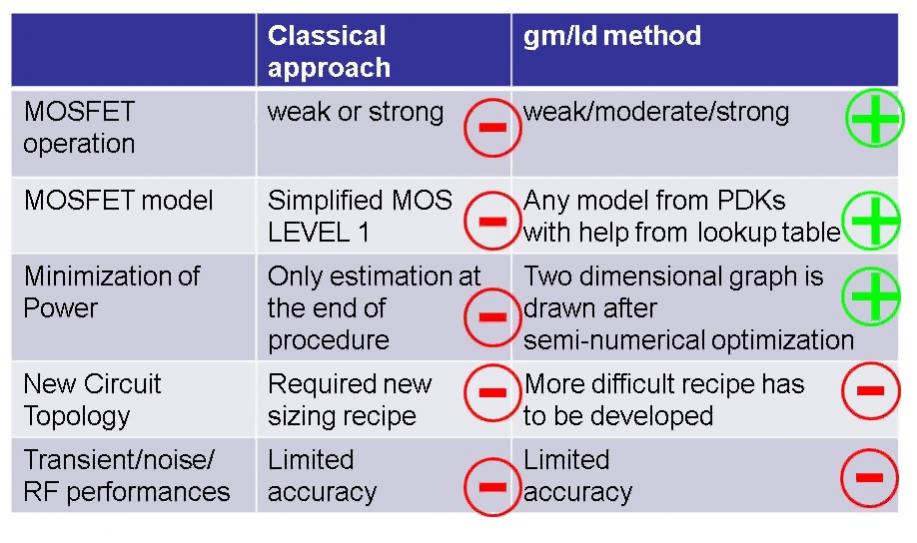

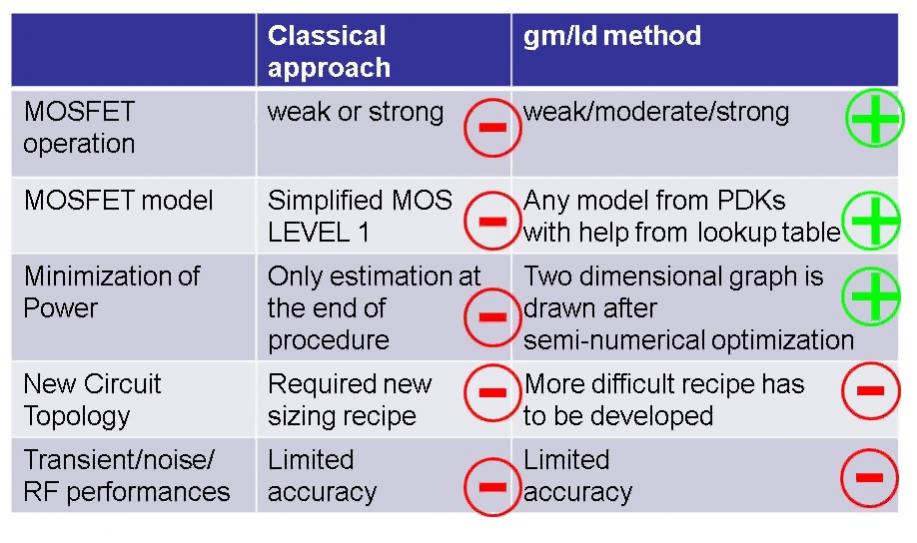

Optimizing for low-power with transistor sizing has several approaches, here’s the summary comparison between the classical and gm/Id methods:

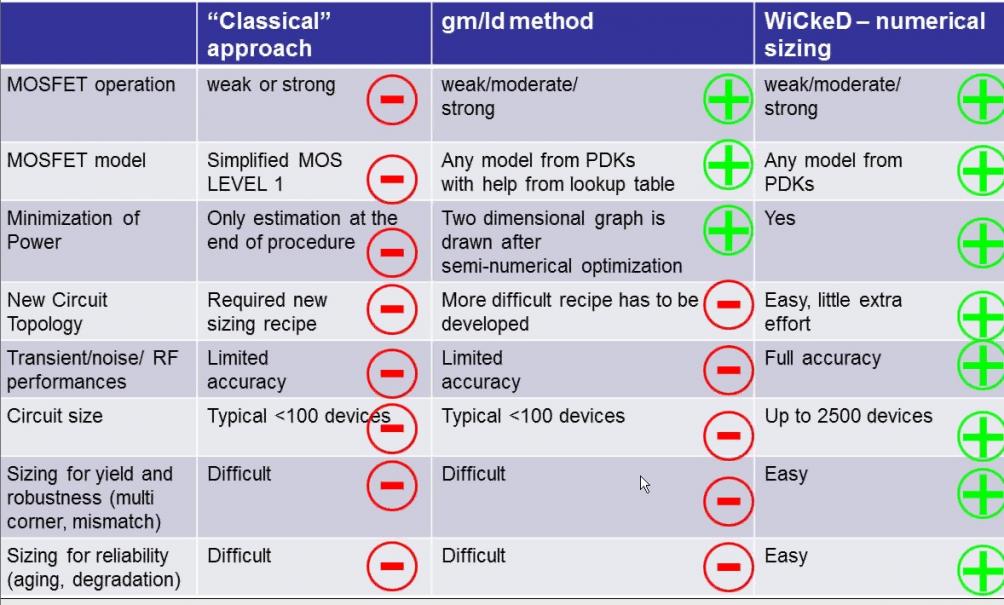

The gm/Id method is an improvement over the classical approach, yet it still has room for more improvement which was a motivator for MunEDA to develop a numerical sizing approach:

The low-power optimization using numerical sizing is part of an EDA tool called WiCKeD.

Some of the benefits of using this automated transistor-sizing tool:

- >500 devices, >50 variables, >10 specs

- Multi-object optimization

- Supports many specs (transient, noise, pss, pnoise)

- Robust sizing (corners, mismatch)

- Reliability sizing (aging, etc.)

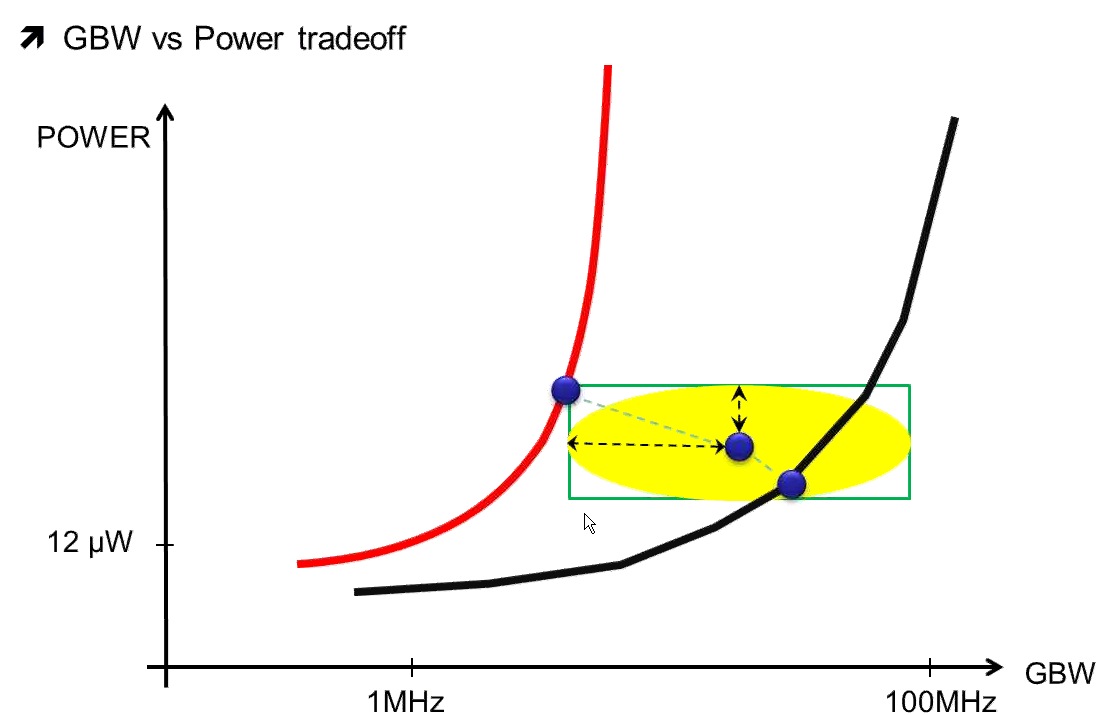

Many analog circuits require the designer to make a trade-off between power and Gain bandwidth (GBW). The following diagram shows how a Pareto curve is used to identify the optimal low-power point for a specific design, where the curve in black is for a nominal process corner and the curve in red shows the design at another process corner.

The theory behind the MunEDA approach for power optimization looks interesting, but who is actually using their tools on real IC designs? The answer is found on a web page listing some 91 customer papers or presentations. In this webinar they summarized five customers:

- Tohoku University – analog design optimization on a pipeline ADC. WiCKeD found lower power consumption, optimized gain, smallest layout area.

- Technical University Dresden – std cell analysis, sense amplifier, clock amplifier.

- Altera – power minimization with multiple Vth MOSFETs in CMOS.

- Fraunhofer – Preamplier for implantable EEG acquisition system.

- Lantiq – nominal vs statistical simulation models, ring oscillator vs technology parameters. Centered their design for yield optimization.

Most webinars that I attend have only a handful of questions, however this webinar from MunEDA had over a dozen questions which really highlights how popular this topic of power optimization is for transistor-level designers.

Webinar Q&A

Q: Your presentation was focused on MOSFET optimization, is the MunEDA solution able to address optimization with non pure CMOS devices, modeled with a custom Verilog-A SPICE model?

Yes, that works.

Q: For only power optimization is there any special feature from WiCKeD?

In DNO you set power to a “min” and keep the other specs in bounds. This setup gives you a power minimization while keeping specs and constraints on all corners.

Q: On slide the WiCKeD GUI appears, and TCL and Python logos were visible. What does it mean, are both languages available?

Yes, both languages are available for batch mode runs.

Q: About the circuit optimization for a given sigma space, is aging also included in that optimization?

Yes, if you have aging models (MOSRA, UDRM or RelXPert).

Q: With respect to Pareto curves in the power/GBW coordinates, the optimum design is selected for FoM = GBW/Power = max? Am I right?

Not exactly. You have two ways: (1) Use linear weights, a*GBW – b*Power = max, or (2) constrained minimization, min Power s.t. GBW=x

Q: Can a dynamic, switched capacitor circuit be optimized as well?

Yes, that is a sweet spot, analytic sizing of switched capacitor circuits can be very hard, but our optimizer handles it well.

Q: A customer test analysis case was done with Tohoku University, a leader in spintronics, do they use your optimizer in spintronic design?

The main application of WiCKeD is in low power CMOS design, which may involve interfaces to spintronic memory elements.

Q: Can WiCKeD handle multiple power/ground domains?

Yes, WiCKeD works on your netlist and feeds it to the simulator. It is very flexible regarding the contents of your netlists and testbenches, simulation algorithms, etc.

Q: Is it possible to watch the presentation again offline?

We will later re-record it in a format suitable for our ELearning platform and make it available there. We will re-run the webinar in June after DAC.

Q: Back to power/ground domains, does that mean that I can have HV and LV devices in the same circuit and WiCKeD will optimize both?

Yes. WiCKeD is routinely applied to I/O circuits such as level shifters. They benefit much from automated sizing.

Q: Speaking about I/O domains, what about ESD devices?

You can include them in your netlist, but I think they are usually not tuned parametrically but rather fixed elements.

Q: Does it give the best Cpk (process capability)? Are the results centered in the process?

There are tools in WiCKeD for yield optimization (although not mentioned in this webinar). This tool can increase Cpk for all specs, including power.

Q: Diffusion resistors at high voltages, can their geometry be optimized considering their voltage coefficients in a switchable (HV+LV) mode of operation or should there be a limited number of use cases specified?

WiCkeD uses schematic properties or netlist instance properties as optimization variables. If the geometry of your diffusion resistor can be set via schematic properties, then WiCkeD can handle it; including callback evaluation to calculate resistor value.

Q: Does the yield optimization account for global, local or both types of variations ?

It is your choice, global/local/both is possible.

Further Reading

MunEDA at DAC

I’ll be visiting with MunEDA at DAC on Monday, June 2nd, their booth is #2213. Let me know if you have any questions that I should ask them.

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.