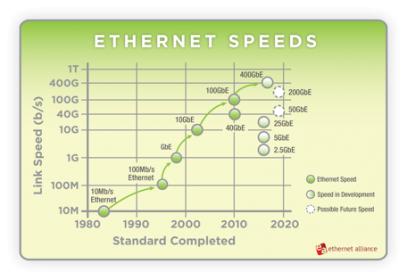

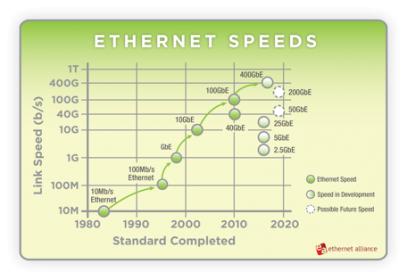

When Ethernet was introduced in 1983 it ran at 10Mbps and mostly relied on hubs and coaxial cable. Twelve years later a faster speed was introduced, running at 100Mbps. Since then we have seen an acceleration of new data rate introductions. According top the Ethernet Alliance, Ethernet could have 12 speeds before 2020, with 6 of those new speeds introduces in the next 5 years.

At the high-end, 25G, 50G and 100G data rates are necessary for supporting the massive growth of internet traffic. The first networks in the 80’s used hubs with very simple circuits and 10’s of ports. Today’s routers and switches have sophisticated network processors that provide numerous services to maintain throughput and manage traffic. The complexity of networking chips is second only to CPU and GPU chips. The number of ports is driving up beyond 256 heading toward 1024.

I find it fascinating that the compute power of the network itself often exceeds the compute power of the things we are connecting to it. The number of gates required is well into the hundreds of millions. With the increasing complexity of network processors comes a need for increasing verification performance. HDL simulators can run at effective speeds of ~100Hz. That translates into only 1,000 packets per day, which is not enough to permit adequate functional verification prior to tape out. The cost of a missed bug is potentially millions of dollars.

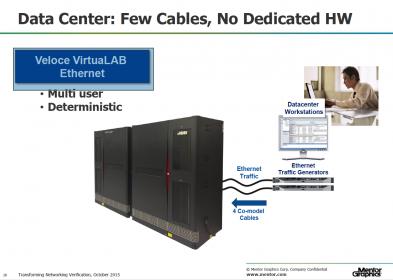

In circuit emulation (ICE) in a verification lab has been the fallback for many companies to achieve better verification. However, this still is not an ideal solution. Huge rat’s nests of cables are required. An engineer often needs to be physically present to set up, fix cables and run tests. Unfortunately, the need to run tests with the system software running on the system hardware remains as critical as ever.

Taking a page from the virtualization trend seen in data centers, Mentor Graphics decided to implement what they call a VirtuaLab for verifying next generation protocols in a tractable fashion. The key to this is using their Veloce hardware emulator to accelerate simulation speed to be able to simulate over 11 million packets per day. Veloce offers visibility and traceability that is not available in ICE approaches. This means that when bugs are found, they are more easily tracked down.

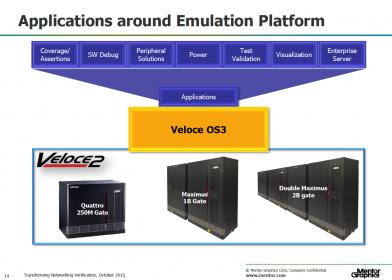

The traditional deal breaker for emulation is capacity. To solve this problem Mentor took the approach of designing their own ASIC, called Crystal 2, for their emulator. Higher capacity per chassis means a cleaner set up in the data center. Their largest configuration supports running designs with 2 billion gates. No tangles of wires connecting boxes are needed. The Ethernet testers can run on a regular workstation and can drive many ports per workstation.

The VirtuaLab is not new, but Mentor just announced support for the latest and highest speed Ethernet specifications, 25G, 50G and 100G. They also provided a lot of customer testimonial information to illustrate the efficacy of the Veloce emulation solution for network chip design.

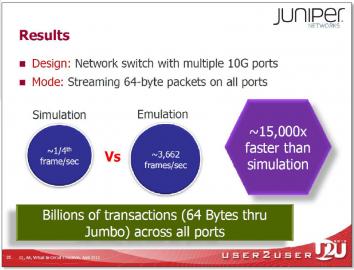

I had a chance to listen to Jean-Marie Brunet, Marketing Director for the Emulation Division at Mentor Graphics discuss the new features in Veloce VirtuaLab. During the presentation he discussed two compelling case studies. The first was Juniper Networks using Veloce to verify a network switch with multiple 10G ports. They were streaming 64-byte packets. They were able to run billions of transactions of 64 bytes up to jumbo across all ports. They went from ¼ frame per second with simulation to ~3,662 frames per second with Veloce. The second case study features Cavium. They were able to go from 1,000 packets per day up to 11 million by switching to Veloce.

Mentor continues to show its prowess in the emulation arena. It’s good to see how emulation can be used to dramatically improve pre-silicon verification of complex hardware-software systems.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.