If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% … Read More

Tag: semiconductor

40nm to 28nm Migration Success Story

The problem:To move dual-port SRAM library and macros from a 40nm process to a 28nm process. In addition to all the changes between two different foundry processes, the 28nm rules are disruptive and incompatible with the previous rules. The memory corecells (foundry-specific) would also need to be completely replaced.

Current… Read More

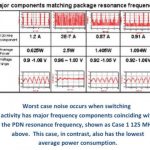

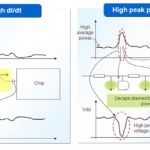

Chip Power Models

As the complexity of the chip-package-system (CPS) interactions has increased, the tradeoffs in doing a power and noise analysis has had to gradually increase. As is so often the case in semiconductor designs, issues first arise as second-order effects that can largely be ignored but each process node makes the problem worse … Read More

Mentor 2 : Carl Icahn 0

The corporate raiders are still throwing rocks at Mentor Graphics. I have followed this reality show VERY closely and find their latest assault seriously counterproductive. Disinformation is common in EDA but I expected more from Carl Icahn and the Raiderettes. They are quite the drama queens. Here is a billion dollar question:… Read More

Ivo Bolsens of Xilinx and Crossover Designs

I was at Mentor’s u2u (user group) meeting and one of the keynotes was by Ivo Bolsens of Xilinx. The other was by Wally Rhines and is summarized here.

Ivo started off talking analogizing SoCs as the sports-cars of the industry (fast but expensive), and FPGAs as the station wagons (not cool). In fact he even said that when Xilinx… Read More

Wally’s u2u keynote

I was at Wally’s u2u (Mentor user group) keynote yesterday. The other keynote was by Ivo Bolsens of Xilinx and is here. He started off by looking at how the semiconductor industry has recovered and silicon area shipments are now back on trend after a pronounced drop in 2009 and revenue has followed. Finally the semiconductor… Read More

Semiconductor RTL Power Analysis: the sweet spot

Power has become the strongest driver of semiconductor design today, more important than area, more important than timing. Whether the device is handheld, like a wireless phone, or tethered, like a router, complex power and energy requirements must be met. Shrinking geometries continue to impose new challenges as power management… Read More

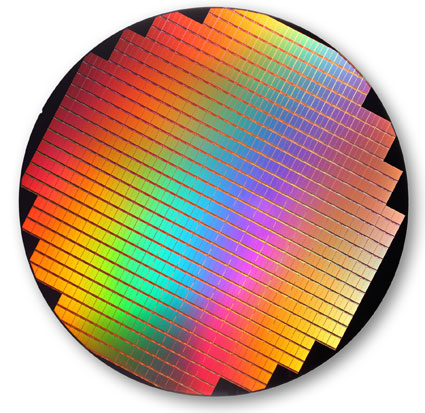

Thanks for the memory

One of the most demanding areas of layout design has always been memories. Whereas digital design often uses somewhat simplified design rules, memories have to be designed pushing every rule to the limit. Obviously even a tiny improvement in the size of a bit cell multiplies up into significant area savings when there are billions… Read More

Intel Buys an ARMy. Maybe

Is Intel in trouble? Since it is the #1 semiconductor company and, shipping 22nm in Q4 this year with 14nm in 2013, it is two process generations ahead of everyone else it is hard to see why it would be. Intel, of course, continues to dominate the market for chips for notebooks, desktops and servers. But therein lies the problem. Pads… Read More

Semiconductor Virtual Platform Models

Virtual platforms have been an area that has some powerful value propositions for both architectural analysis and for software development. But the fundamental weakness has been the modeling problem. People want fast and accurate models but this turns out to be a choice.

The first issue is that there is an unavoidable tradeoff… Read More