Probably everyone knows that openAccess is a layout database. It was originally developed at Cadence (called Genesis) but has since been transferred to Si2. Strictly speaking, openAccess is actually an API and the database is a reference implementation. The code is licensed under a sort of halfway to open-source: you can use … Read More

Tag: semiconductor

Can Your Router Handle 28 nm?

With the adoption of the 32/28 nm process node, some significant new challenges in digital routing arise—including complex design rule checking (DRC) and design for manufacturing (DFM) rules, increasing rule counts, very large (1 billion transistor) designs. To meet quality, time-to-market, and cost targets, design teams… Read More

HSPICE gets Faster, better Convergence

Hany El Hak – Product Marketing Manager

Frederik Iverson – AE

Scott Wetch – HSPICE Architect

HSPICE – 5 years ago convergence was not so good, while 95% of analog circuits today converge out of the box, no options are required.

Synopsys AMS Portfolio – wide range of tools

– Custom Designer: IC schematic and layout tools

–… Read More

Sagantec 2 Migrate iPad2s @ #48DAC

Sagantec is the leading EDA provider of process migration solutions for custom IC design. Sagantec’s EDA solutions enable IC designers to leverage their investment in existing physical design IP and accomplish dramatic time and effort savings in the implementation of custom, analog, mixed-signal and memory circuits… Read More

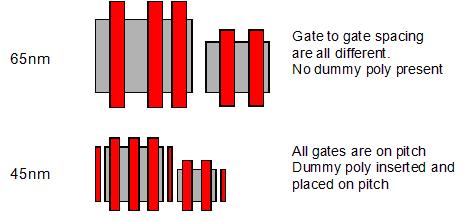

65nm to 45nm SerDes IP Migration Success Story

The problem:To move a single lane variable data rate SerDes (serializer-deserializer) from a 65nm process to a 45nm process, achieving a maximum performance of up to 10.3 Gbps. This is a large piece of complex mixed-signal IP with handcrafted analog circuits. Circuit performance and robustness are critical and must be maintained… Read More

3D IC @ #48DAC

A three-dimensional integrated circuit (3D IC ) is a chip in which two or more layers of active electronic components are integrated both vertically and horizontally into a single circuit. The semiconductor industry is hotly pursuing this emerging technology in many different forms, as a result the full definition is still somewhat… Read More

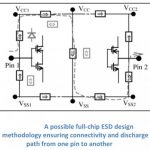

Analyzing and Planning Electro-static Discharge (ESD) Protection

ESD has historically been a big problem analyzed with ad-hoc approaches. As explained earlier, this is no longer an adequate way to plan nor signoff ESD protection.

Pathfinder is the first full-chip comprehensive ESD planning and verification solution. It is targeted to address limitations in today’s methodologies.… Read More

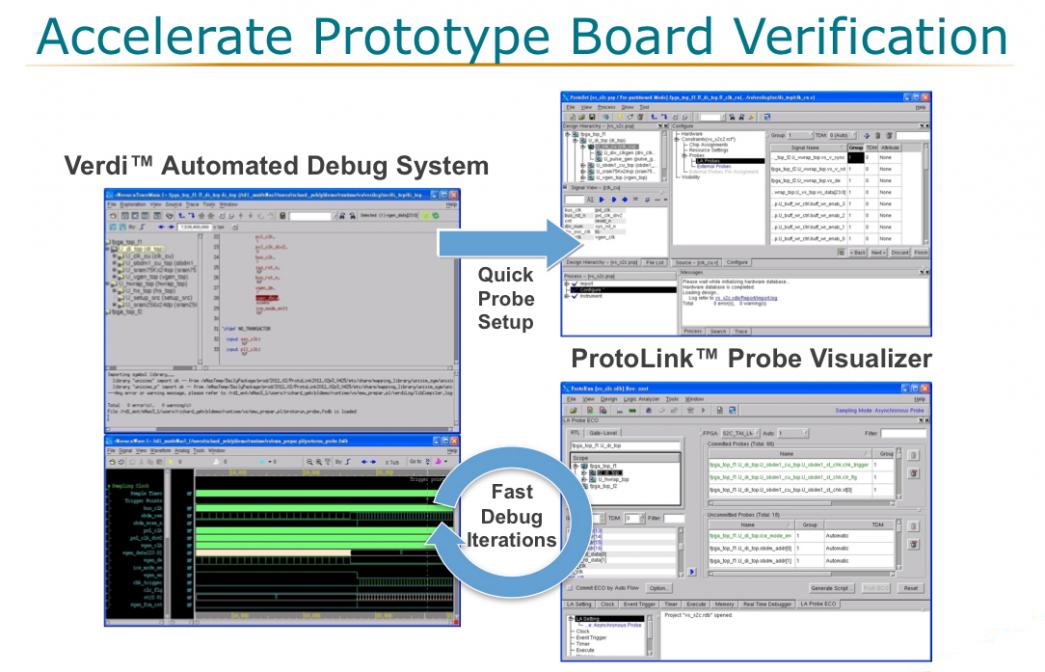

FPGA Prototypes Made Easy

FPGA-based prototype boards are a fast, cost-effective platform for SoC system validation but they are notoriously difficult to set up and to debug. There is a big upside, however, allowing early software integration and testing and thus finding bugs in both the software and the SoC earlier. This approach is much cheaper than … Read More

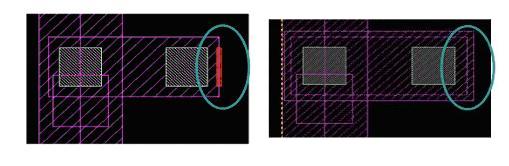

Adjusting Custom IP to Process Changes

A High-Definition Multimedia Interface (HDMI) IP core was being implemented in an advanced process technology. This fairly large and complex analog mixed-signal (AMS) IP comprising over 130K devices was close to being finalized and shipped to the customer. But many design rules at the foundry were unexpectedly changed from… Read More

SOC Realization: How Chips Are Really Designed

If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% … Read More