If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% to design, which might be 100 milliion gates, a non-trivial task. But increasingly there is a mismatch between the classic EDA flow and the way systems are actually put together out of blocks of predesigned IP, microprocessors, memories and pre-existing software operating systems and stacks.

If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% to design, which might be 100 milliion gates, a non-trivial task. But increasingly there is a mismatch between the classic EDA flow and the way systems are actually put together out of blocks of predesigned IP, microprocessors, memories and pre-existing software operating systems and stacks.

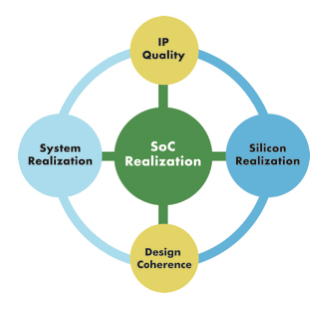

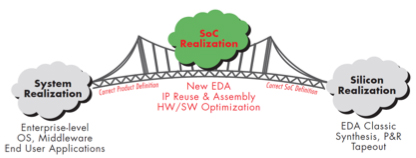

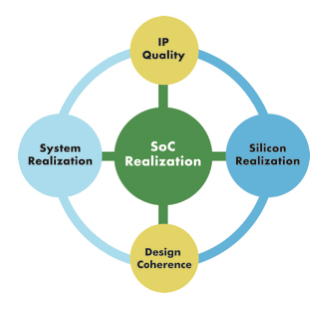

SoC reallization is the bridge between traditional EDA flow for creating a design from scratch and the IP and software-centric world of designing a system. Since most design is done this way, this is likely to be an area of technology that will play a major role in the years ahead.

A chip being designed will typically contain a lot of the previous generation of the chip, and especially a lot of the previous software of the chip. Software tends to be much longer lasting than hardware, enduring for decades whereas hardware lasts for just one process node before being re-designed.

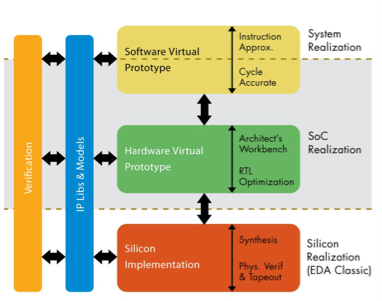

SoC Realization is taking design up to the next level and thus being able to analyze and verify design concepts much earlier in the design process in order to avoid costly errors or excessive iteration downstream. It ties downwards into the silicon implementation realm and upwards into the software world.

There are three critical areas driving todays’s IP-based SoC Realization solution:

There are three critical areas driving todays’s IP-based SoC Realization solution:

- IP sourcing: Quality metrics? Silicon proven in which processes/foundries? Power, performance, area, license fee?

- SoC creation: Optimality of architecture, software/hardware interface, scalability across product generations?

- SoC handoff: Is the SoC ready for implementation? Will it meet specs? Can impact of system decisions be measured?

- Continuous model fidelity: at all levels of abstraction from software virtual platform down to silicon implmentation, is the fidelity of the model maintained? Is system intent correctly preserved as the design is reduced to more silicon-specific implementations?

Read the Atrenta white-paper on SoC Realization here

*Note: to read/write comments you must log in.

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!