EDA tool development is always pushing the boundaries, driven in part by bigger, faster chips and more complex IP. For several years now, the trend has been developing tools that spot problems faster without waiting for the “big bang” synthesis result that takes hours and hours. Vendors, with help from customers, are tuning tools… Read More

Tag: aldec

Aldec Verifies Compatibility of Northwest Logic’s PCI Express Cores with HES-7™ SoC/ASIC Prototyping Platform

Henderson, Nevada – July 11, 2013 –Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification solutions, today announced that engineers incorporating high-speed PCI Express data transmission into their SoC and ASIC designs can accelerate their time-to-market utilizing Northwest Logic… Read More

HW Prototyping and HLS at DAC

I love it when EDA companies send their engineers to DAC because I learn more of the unvarnished truth about their products. I met with Bill Thomas of Aldec to get an update on their HW prototyping boards, then two NEC engineers to learn about High Level Synthesis.

HW Prototyping

Bill Thomas, Research Engineer at Aldec

… Read More

Missed #50DAC? See Aldec Verification Sessions Online

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

Advanced Verification – HW/SW Emulation – SoC/ASIC Prototyping

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

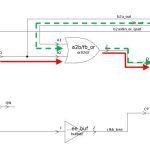

The never-ending quest to kill metastability

The difficulty of an engineering problem can be gauged by two things:

1) The number of attempts to generate a solution.

2) The degree of hyperbole used to describe the effectiveness of the latest solution.

The problem many folks in the EDA industry are after right now is clock domain crossings (CDCs) and the resulting metastability… Read More

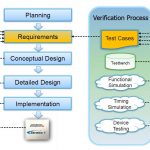

It’s all in the details of FPGA requirements management

Word association: if I said “requirements management”, you’d probably say IBM Rational “DOORS,” or maybe Serena or Polarion if you come from the IT world. But what if the requirements you need to manage are for an FPGA or ASIC, with HDL and testbench code and waveform files and more details backing verification, and compliance… Read More

UVM/SystemVerilog: Verification and Debugging

At DAC in just three weeks you can learn about which EDA vendors are supporting the latest UVM 1.1d (Universal Verification Methodology) standard as defined by Accellera. One of those EDA vendors is Aldec, and they have a 45 minute technical session that you can register for online. Space will fill up quickly, so get signed up sooner… Read More

A random walk down OS-VVM

Unlike one prevailing theory of financial markets, digital designs definitely don’t function or evolve randomly. But many engineers have bought into the theory that designs can be completely tested randomly. Certainly there is value to randomness, exercising all combinations of inputs, including unexpected ones a designer… Read More

Prototyping Over 100 Million ASIC Gates Capacity

Most SoCs today are being prototyped in FPGA hardware before committing to costly IC fabrication. You could just design and build your own FPGA prototyping system, or instead choose something off the shelf and then concentrate on your core competence of SoC design.

Thanks to the FPGA vendors like Xilinx we now have FGPA prototyping… Read More