You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Most programmers can read a code snippet and spot errors, given enough hours in the day, sufficient caffeine, and the right lens prescription. As lines of code run rampant, with more unfamiliar third-party code in the mix, interprocedural and data flow issues become more important – and harder to spot.

Verification IP particularly… Read More

Back in the days where computing was dominated by a few big (and now mostly dearly departed) names, there was a saying: “Nobody ever got fired for buying IBM.” The relative safety of immediate brand recognition, especially among non-technical upper management, dissuaded many users from recommending or even seeking out other … Read More

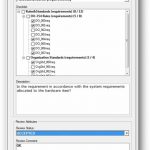

Engineers are known for their attention to detail and precision in thinking, but sometimes still struggle during compliance audits. This is especially true the longer a list of requirements becomes, especially unstructured lists kept in spreadsheets and on Post-It notes.

It gets even more complicated, because in defense circles… Read More

Social Media at Aldecby Daniel Payne on 01-09-2014 at 5:38 pmCategories: Aldec, EDA

I’ve been blogging about EDA and Semiconductor companies using social media to create new ways to talk and listen to engineers, so today I looked at Aldec and how they are using social media. Aldec offers EDA products for: FPGA Simulation, functional verification, emulation, and MIL/Aero verification. Their Home page … Read More

Our popular smart phones have a whole slew of RF-based radios in them for: Bluetooth, WiFi, LTE, GSM, NFC. Using just a single clock frequency for a DSP function or SoC is a thing of the past, so the design of multirate systems is here to stay. So now the challenge on the design and verification side is to use a methodology that supports:… Read More

SystemVerilog as an assertion language improved and simplified with the 2012 version compared to the 2005 version. I recently viewed a webinar on SystemVerilog 2012 by consultant Srinivasan Venkataramanan, who works at CVC Pvt. Ltd. There’s been a steep learning-curve for assertions in the past, and hopefully you’ll… Read More

One of the present ironies of the Internet of Things is as it seeks to connect every device on the planet, we are still designing those things with largely unconnected EDA tools. We may share libraries and source files on a server somewhere, but that is just the beginning of connection.

It is not surprising that synthesis tools from… Read More

In one of my favorite movies, Brad Pitt utters the only question that matters in baseball or technology management in the face of uncertainty: “Okay, good. What’s the problem?” Not surprisingly in that scene, as the question circles the table of experts used to doing things the old way, not a single one can answer it correctly in the… Read More

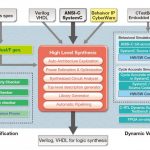

Perhaps no area in EDA has been as enigmatic as high-level synthesis (HLS). At nearly every industry event, some new-fangled tool always seems to be tabbed as the next big thing by some analyst or pundit. In a twist, the latest news is on one of the oldest tools – CybeWorkBench.… Read More

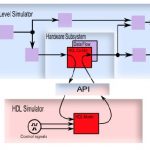

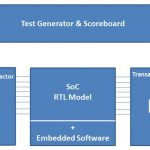

There never seems to be enough time in a SoC project to simulate all of the cycles and tests that you want to run, so any technique to accelerate each run is welcomed. You can just wait for your software-based RTL simulator to finish running, or you can consider using a hardware-based accelerator approach. I learned more about one such… Read More